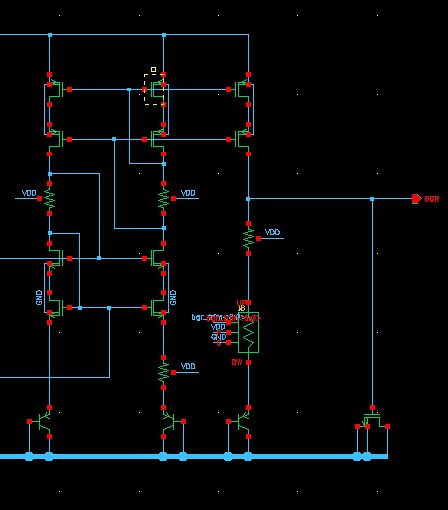

Bandgap的PSRR问题请教

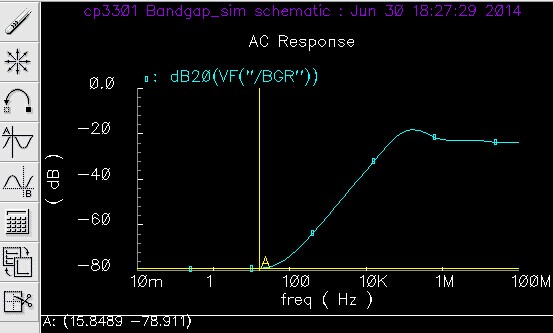

bandgap结构如上图,仿真后PSRR只有在频率15的时候为80dB,如何不提高电路功耗 ,

可以增大带宽?

没有人看见么,自己顶起来

调节输出上面两个P管,vds越大越好,注意衬底连接

谢谢,如果我增大了vds,流过两个pmos的电流会减小,前两路的流过三极管的电流与输出端的电流会有很大差别,这样在流片的时候,是否会引起die to die的很大差异

说明N管不饱和了,所以你这个结构要全corner都ok,电源至少要1.8以上,如果能再高点那么就比较容易做PSR,否则很难。可以换结构用运放

现在仿真corner,所有管子都处于饱和状态,有点害怕流片后,偏差更大,以前遇到过这个问题。这个是用在电源管理芯片,对功耗要求很严格,如果用运放的结果,功耗卡不下来。

mc仿一下就大概知道了

好的,多谢

現在耗多電流呢?

总体不到3u

你最大耗電要求多少uA?

最大就只能3u,现在是2.5u,用在电源管理,不能大了

请教下小编哈,这个结构的PSRR如何推导?

沒有OP,那gain就太小,就沒有機會了,那只能輸出端放大電容了。

还有问下小编,你的仿真电源电压是多大

请问小编,为什么增加vds能提高psr啊?新人请指教

简单来看,要psrr好就是电源对输出影响小,也就是电流镜阻抗和下面阻抗的分压问题,下面不变的话,电流镜阻抗越大越好,通过相同的电流,电压大阻抗就大

谢谢小编的答复。增加vds是不是会增加电流啊?id=1/2*k*(Vgs-vth)2*(1+lamda*vds),而ro与id成反比。这样会使上面cascode管子电阻减小。请问我的理解哪个地方有问题啊

ID不变,改变K*(Vgs-vth),vds就会相应变化,PSR是大信号不看avds/aid,看VDS/ID

谢谢你的耐心回复!明白了!应该是拉扎维483页的图吧

学习了

为什么PSR是大信号,能解释一下吗?新手