高手帮我看看流水线ADC里的运放是否建立到位?

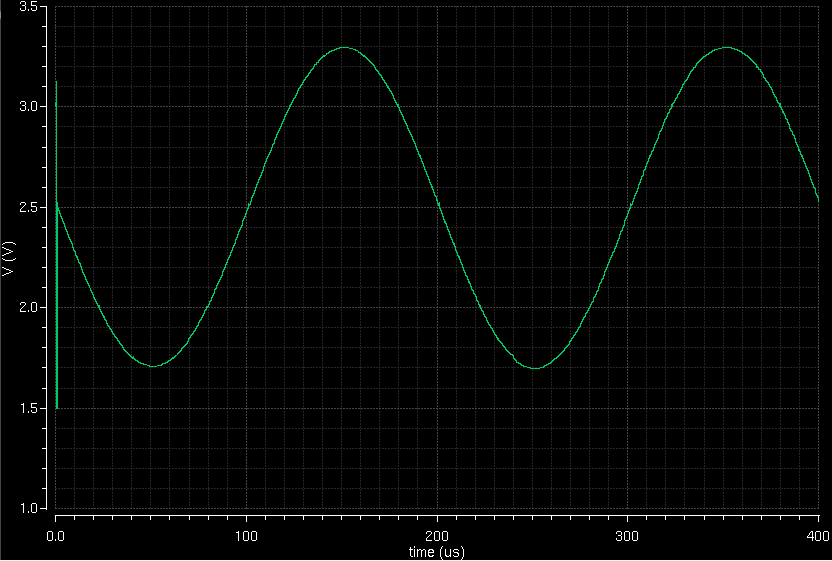

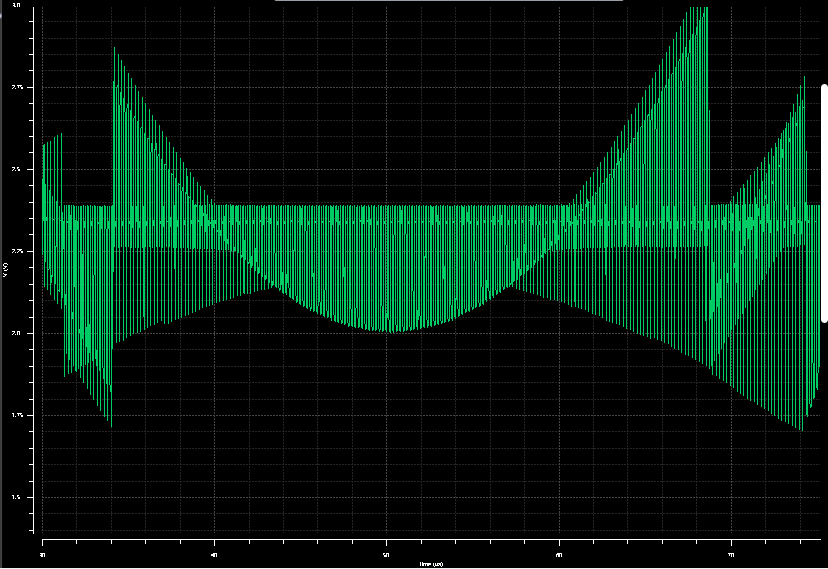

最近做了一个流水线ADC,输入正弦波,再用理想的DAC转换成模拟波形,如下图

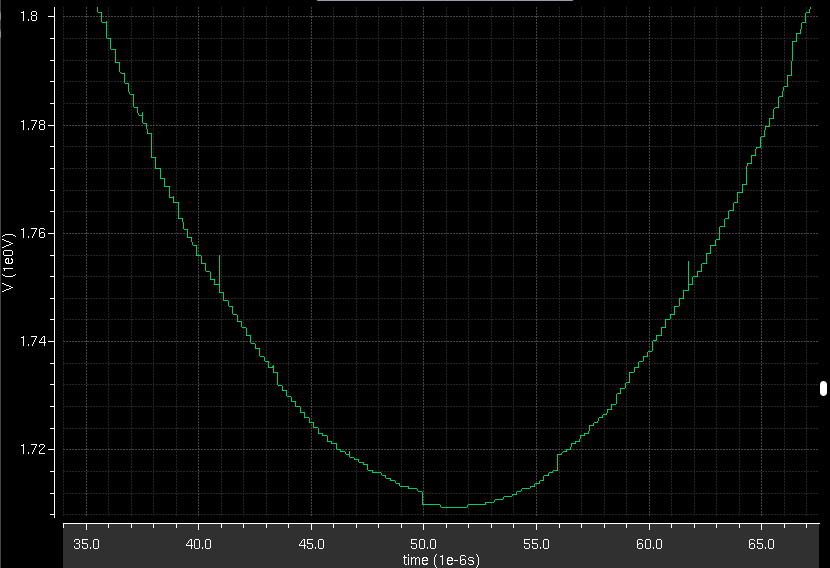

将细节放大后,发现波形失真,好象输出数字码比正常者值要小

波形失真的原因是不是MDAC里的运放建立不完全?设

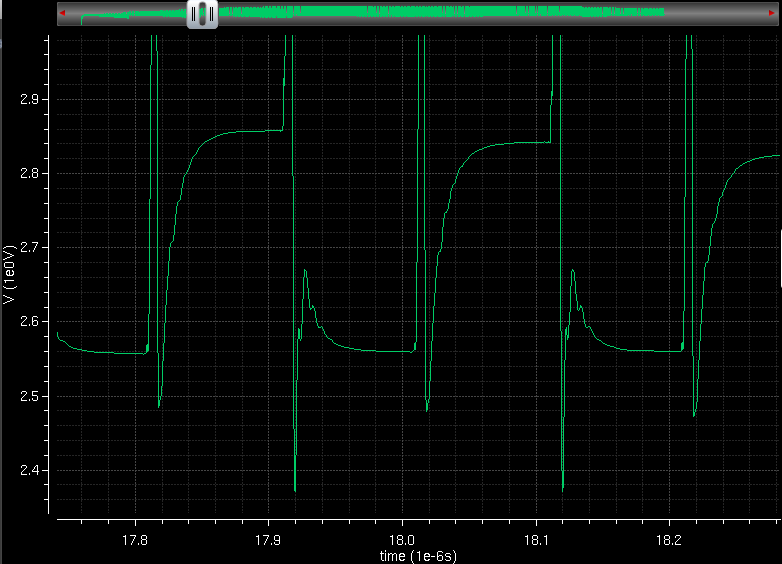

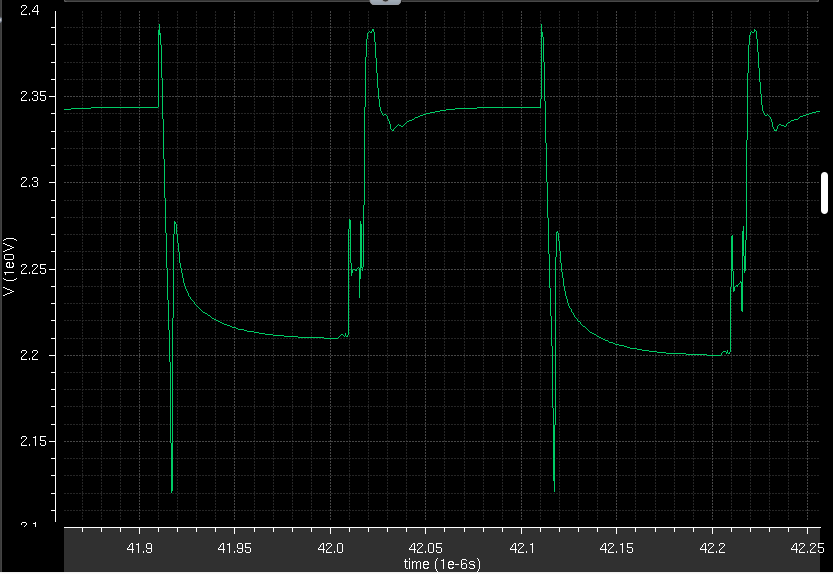

设计方案里采用了2.5Bit MDAC和1.5Bit MDAC,建立过程如下图:、

(2.5Bit MDAC建立过程,见上升沿)

(1.5Bit MDAC建立过程,见下降沿)

请高手帮我看看,MDAC的运放建立是否完全?误差是否在设计合理范围内?

运放建立正常的依据是什么?

另外,MDAC的输出波形里有很多很大的毛刺?是否正常?

如何消除这些毛刺?

谢谢

谢谢

1. 总的ADC多少位?一般如果12位,第一级2.5bit的话,运放需要建立的精度需要在10位精度0.5LSB以内。

2. 输入范围Vpp=1.6V? 电源电压5V? 运放什么结构,输出摆幅是否够?

3. 运放相位域度多少?

看起來有missing codes,gain error太大!

1、 ADC是12位,输入信号幅度是+/- 1V,第一级MDAC输出要10位0.5LSB,误差电压是不是需要1/2^11=0.0005V?

2、第一级2.5b MDAC运放是带增益自举的折叠共源共栅运放,后面1.5b MDAC是折叠共源共栅运放,电源电压是5V,输出摆幅1.5-3.5V应该足够

3、第一级运放相位裕度好像70度

是运放的增益误差太大是吧,SHA和第一级2.5b MDAC的运放增益是105dB,后面大概是85dB。是不是因为在采样时间内信号建立不完全?

请问SHA的建立误差是不是要做到1/2^13=0.0001V? (信号是2.5+/-1V),第一级MDAC的误差小于1/2^11=0.0005?后面逐级增加?

非運放增益誤差太大,是指MDAC's transfer function -> Vout=G*(VIN-Vdac)的gain "G" 誤差太大,其誤差來源主要是 finite OP gain, finite settling time 及 capacitor matching.

你的運放增益足夠,如果仿真時VREFP,VREFN是採理想電壓源,那就仔細檢視因settling time不足導致信號建立

不完全的gain error.

SHA建立誤差的規格合標準,第一級MDAC的規格約佔1/16LSB的DNL誤差.

也可以看下是不是两相不交叠时钟的不交叠时间太长了

帮你顶一下

同求…………………………

学习学习

learn of this !

同问,谢谢

Gooooooooooooood。懴馟蕫枌謬

信元不够了。

你为什么把直接对ADC 交流输出结果做FFT,看SNR和THD呢? 用个DAC转回来,似乎更麻烦,当然DAC理想的话,应该是没有问题的。

Gooooooooooooood。玁宯樥凥嗚