AC-DC中bandgap的PSRR问题

自己顶一下。请各位大神稍微点拨一下,谢谢了

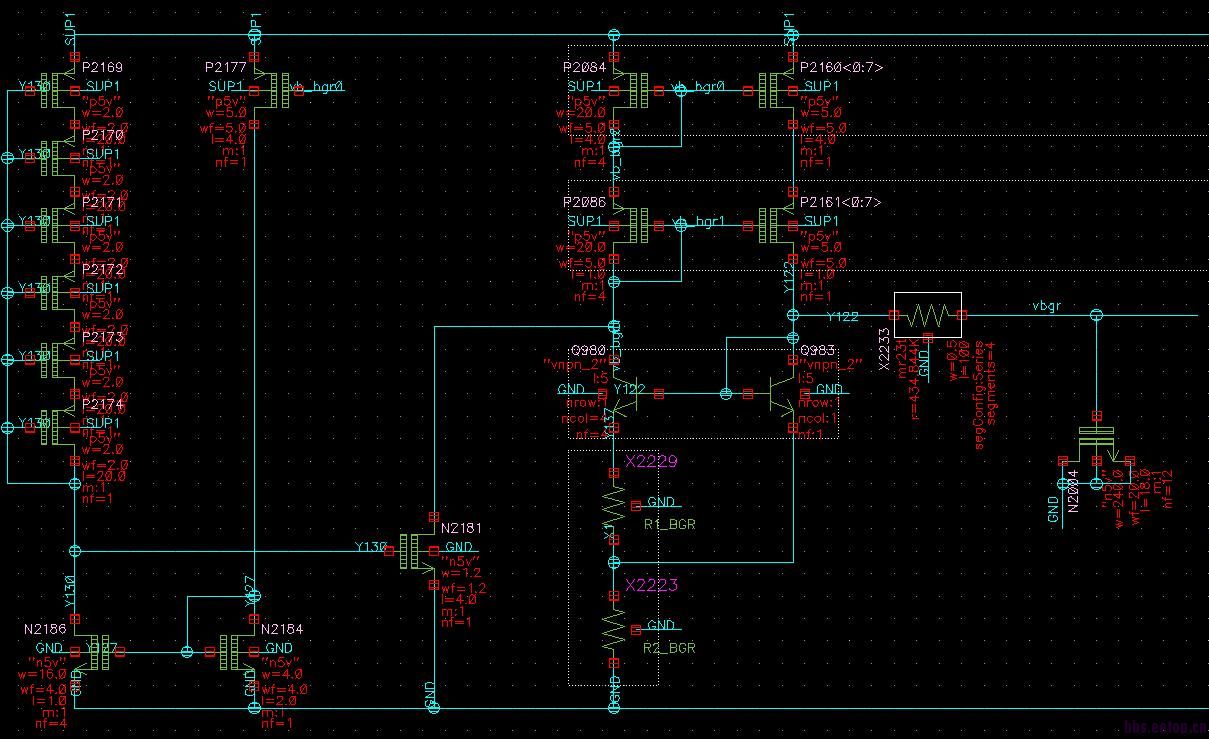

结构贴出来看看

标题

我就是想知道,要不要考虑开关频率处的PSRR,或是考虑多大频率的?这样我才能知道怎么改,以及要不要换个结构

坦白讲,小编的担心是很有道理的

通常bg的输出会适当加一些rc去滤波,这个位置上也可以理解成提高高频psrr

以小编200k -2db为例的话,如果增加一个10k左右的极点,因该会有将近-30db

这样的好处是不用改动已经设计完的bg

坏处是,10k对应的rc,面积还是不小的

另外psrr-,如果做成current mode,会好很多

但是通常是通过良好的gnd规划来回避这个问题吧。

太感谢了!再请教下,您说得current mode是指哪种结构?

比如 banba

Bandgap做得太差,打回去重做。:-)

一般带宽做到1MHz很正常,最差的PSRR也要有-20dB。小编有仿真运放的特性吗?

你bandgap输出VREF有没有pin呢? 有pin, pin上挂个100nF或者1uF电容就可以好很多了。

没有这个pin的话,还是band gap上改进吧。

感谢指导!您说的带宽1MHz指的是哪个带宽?是PSRR下降完开始上升时的频率?开关频率如果200k左右的话,PSRR到底要做到什么程度算合适呢?

我的bandgap是不带运放的结构,如下图,为了提高PSRR,我把输出的RC提高了,目前在开关频率附近10dB左右,我看不出来还能怎么提高了(不显著增大面积),除非改结构,希望您指导一下。

这个输出只是片内用的,不接pin,电路图我放到10楼了,请指导

多谢你的贴图。

如果有运放的话,带宽就是环路的stb分析中的GBW频率,一般可以到1MHz。

-10dB就只有3倍。就是说如果电源上有一个0.1V的纹波,那bandgap就有33mV的抖动。我感觉还是太大了。

无运放的Bandgap是性能比较差。一般PSRR低频处靠环路的增益,高频处靠负载电容。可以考虑换结构加个运放。你们对功耗要求很高吗?50uA就可以了。

还可以在电源上加RC低通滤波,不过也耗面积。

回复 10# ygyg100

多谢指点啊!

标题

确实对功耗要求比较高,电流只15u,真是太感谢了!