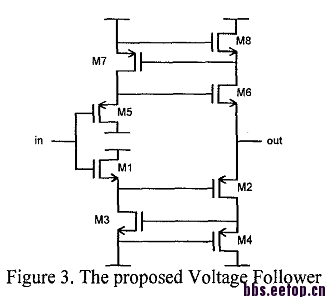

关于一个简单的buffer电路的输出阻抗的求解

貌似不是哦,上下两个都组成了威尔逊电流镜,输出电阻的数量级应该是gm2rds3级的,你可以看看allen的书里有写

我怎么觉得输出阻抗就是1/gm呢。没啥特别的啊

好像不是,乍一看也以为是1/gm (只看上半边电路),但仔细考虑偏置电流不确定

这是一个自偏置,让M5、M6 VGS相等,电流大小是M6决定的,有一个loop gain=1的负反馈(从vo往上绕一圈回到vo),输出阻抗应该是(1/gm6)/(1+LG) = 1/2 1/gm6

应该不是,M8和M4实际都是一个MOS二极管的接法,M2,M3,M4和M6,M7,M8分别构成了NMOS和PMOS的威尔逊电流镜,M1和M5是提供输入电流的,所以他的输出阻抗是两个威尔逊电流镜的并联,具体分析在allen书里电流镜一章有仔细提到。

M3引入一个负反馈,下边是(gm1*gm4-gm2*gm3)*(1/gm2)*1/(gm1*gm4),上边类似;

你说的对,可是我觉得1/gm和1/gm/2差不多啊。而且你的推论也是NMOS和PMOS的VGS相等才行,否则直流偏置点不会一样。而实际上,直流偏置点肯定会不一样。但是无论直流工作点如何不一样也不会对1/gm做出可观的增加,这种负反馈的计算不是很有意义。所以就大约估计了一下。

我开始是观察法没具体推导,假设gm2=K*gm4,gm1=K*gm3,代到你的结果里阻抗是0!

然后我推了一边,你的结果又没错

这个地方不是负反馈,而是正反馈……按我的假设增益为1,阻抗被bootstrap掉了,这个电路有意思啊

不是威尔逊电流源吧,哪有PMOS和NMOS做镜像的。输出阻抗的计算是让输入电压接地,因此你可以再看一下,当输入电压接地时,从输出灌进一个电流,输出电压会有像电流源那样大的变化吗?

不是假设M7、M8的VGS相等,而是专门把他们接成相等,这样两路的电流会不等,从而能够让M5、M6的VGS与M7、M8匹配而相等,让crossover影响变小

反馈我看错了,是正反馈。

对,我的意思是这样:

第一,这个电路的重点是实现输出等于输入加上一个Vgs再减去一个Vgs,而不是对输出能力再1/gm的基础上再进一步推挽。把1/gm变成1/gm/2没有本质的进步;

第二,这个电路实际上也不是肯定能够保证两个Vgs相等。因为在比较轻载的时候,很有可能M8的Vgs小于M7的Vth,因此这个电路是不完整的,需要添加另外一个直流偏置电路。这样应该说M7和M8的Vgs肯定是不相等的。真反馈环路也应该是小于1的,不然不可能实现ClassAB的功能而会有交越失真。

Mark,好题

考察上半部分,

1)输出阻抗(低频)=1/gm6-gm7/(gm8*gm5),它可以远远<1/gm6,甚至=0,甚至为负,wind2000sp3的观点1是错误的

2)环是正反馈,环路增益=gm7*gm6/(gm8*gm5*(1+gm6*RL)),它可以=1,<1,>1,注意它和负载RL有关。环路增益<1时才能稳定,当环路增益>1时,输出阻抗为负。

考察全部,

1)这是一个类classAB buffer,在上下部分都工作时,输出阻抗/2(近似)

2)大信号或RL变化时,因为镜像电流成比例,Vgs动态同方向变化,Vgs的差虽然不能为0,但能保持低值,实现跟踪。

谢谢大家的关注,这个电路时96年ieee的文章,主要为了提高buffer的性能,比如降低输出阻抗,稳定接近于1的增益(这个有点不是很突出),提高速度等等,分析电路,上下对称,我们只看M1、M2、M3、M4,M1和M2构成复合管,作为电压跟随mos管来用,M3、M4为负反馈电流镜,主要作用有两个,1、电流镜的作用,为支路偏置,2、电流镜负反馈,减小输出电阻,或者说增大复合管的垮导,3、用来稳定增益,减小输入到输出的电压offset。首先我们来计算垮导,这个问题我发过帖子,gm1*(Vin-Vs1)=I1,I1=-Iout,Gm2*Vs1=Iout,化简,这种求法是近似计算,Gm=gm1*gm2/(gm1-gm2)通过调整gm1和gm2的值,可以获得很大的垮导或者很小的输出电阻。再来分析第三个作用,不知道有没有说清楚,希望大家理解

mark 好题

请问那篇文章叫什么题目呢?