求教:全差分的单位增益放大器版图画法

此外如果加上共模反馈和偏置电路,此时电路图上已经不对称,如何在版图上取得对称匹配的效果

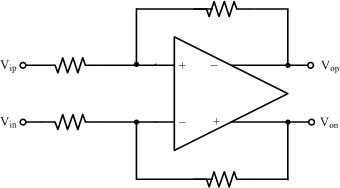

图2

就图而言还是要对称画的!

凡是差分对都要对称画

你是post-simulation? 仿真能看出工艺/版图导致的offset 吗?

是不是你的systemic offset?那是由于电路而不是layout 引起的

是post-simulation,做过寄生参数抽取,应该是电路连线不对称造成的,用schematic仿真是没有offset的。

现在想问怎么在版图中加上偏置电路以及共模反馈,感觉加上以后很难实现完全对称

具体是什么样的应用啊,是连接成反馈形式吗

layout上会影响dc-offset的因素主要是寄生电阻

你shematic闭环仿真过吗,如果闭环仿真没有发现有系统offset,那么完全肯定由layout引起dc-offset

你既然抽了寄生,反标到网表中应该可以看到啊

看看哪个寄生对dc-offset影响较大

是接成的这种形式,在这种闭环仿真下有4mV的dc-offset,开环仿真是大概2V的dc-offset,因此必须要对版图进行改善

我是用assura抽取的寄生参数,看到的是一个类似版图的av_extracted文件,用它做的后仿,从这上面看寄生参数很头大啊

在这种闭环仿真下有4mV的dc-offset,开环仿真是大概2V的dc-offset?

是什么意思,2Vdc-offset?

觉得你这样高输出阻抗的opamp带电阻负载要考虑一下它本身的Rout形成闭环后的rout是否比反馈电阻足够小

不影响opamp的开环dc gain及开环设计的性能

还有你指的post-simulation的dc-offset是指你差动输入vin,vip都输入相同的dc电压,如2V

测输出vop,vop的差值,或者直接看v+,v-的差值?

还是在加交流差分信号后,看到v+,v-的差值?

差分输入差分输出的opamp好像在闭环状态不存在系统dc-offset,除非你opamp两边不对称(在schematic和layout时候)那样你过不了lvs,这种情况应该不会发生。

2V的dc-offset是指直流零输入状态下,正负输出端电压差为2V。我也不知道为什么这么大,前两天有些忙,明天有空再去看看

rout倒是没有问题,输出增益是电阻的比值。另外我用别人的差分版图做后仿,dc-offset也是存在的,只是小很多而已,闭环dc-offset大概在uV量级

您好,我现在也遇到了同样的问题:全差分运放post_simulation时(带RC寄生参数)。开环仿真(只是在输入对管加上直流电平),发现输出端有2V左右的dc-offset(即VOP-VON=2V),而增益相位等都没变,管子仍在饱和区。又跑了一版(不带寄生电阻的后仿)后发现,这个问题就不存在了。但是寄生电阻也不是很大啊。是不是我设计的运放鲁棒性不够呢,还是版图的影响却是很大。请问您当时是怎么解决这个问题的呢,不胜感激。

请问小编后来这个问题是怎么解决的?

最近我也设计了这种两极米勒运放。后仿发现直流偏置点在输出端的电压并不是预期的800mv。 但是各个管子都是工作在饱和区,实在是很费解。

你这个问题和我之前说的问题是两码事,之前的问题好多年,忘了,应该是工艺PDK的问题吧

输出共模偏离预期值几毫伏是比较正常的事,一般是由于共模负反馈电流镜像不准确造成的,如果对这个要求高,可以改下共模反馈的管子,用共源共栅应该会好些

谢谢小编的回答,已经找到问题了,是版图画的不对称的原因。

我也是这个问题,有没有人能解答啊