ESD 设计的一些探讨

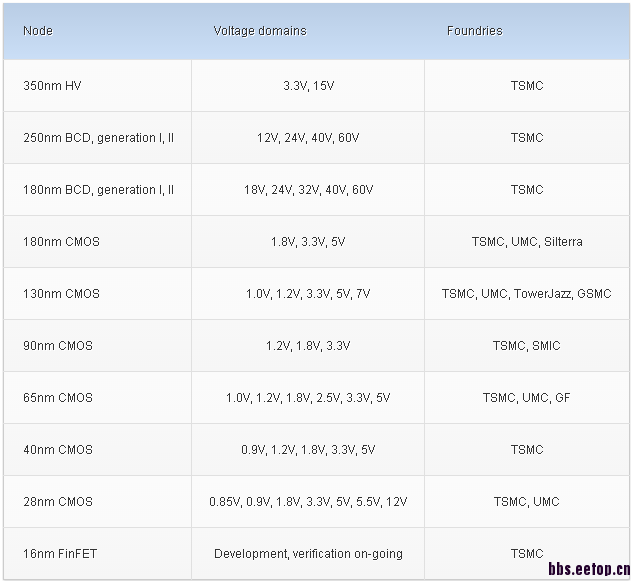

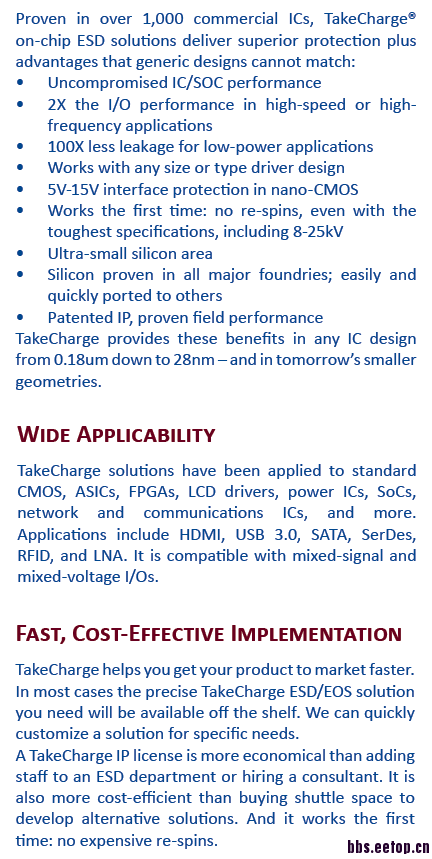

随着IC先进制程技术的应用, 芯片功能的增多和尺寸的减小, 对于半导体厂和设计公司来说, 不断面临着产品对静电保护ESD提出的越来越高的要求. 欧洲ESD和EOS 领域的有些资深企业, 早已成为TSMC IP中心, 设计中心的联盟成员, 也是UMC的合作伙伴, ESD IP覆盖一直到了28nm的先进工艺制程. 与此同时, 在新的工艺平台SOI, 3D-IC, FINFETs方面, 也提出了创新的ESD解决方案.ESD支持方面, 主要涵盖了在先进工艺平台方面, 高速电路, 无线射频界面,特别耐高压等设计方面, 以及在特殊环境应用领域的汽车电子, 工业产品方面的ESD问题探讨和设计培训, 让客户更清楚得了解在高密度, 小型化, 复杂功能电子设备设计的背景下, 如何实现减少ESD 设计面积, 设计时间,提高IC 性能和完成苛刻的ESD/ LATCH-UP, EOS等各项指标的要求. 目前支持的所有Si-PROVEN IP 如下表, 因为ON-CHIP ESD 技术有灵活可移植性, 在几个星期内可以到任何半导体厂的工艺节点传输, 如果需要私人定制, 也是效率非常之高. 如果有什么ESD问题,也能很快解决.国内的设计公司和半导体厂也应该积极行动起来, 在ESD这个领域, 有更好,更专业的公司出现.

Better IC/SOC performance with lower cost:

Low Cost, high voltage solution to meet system level ESD/EOS requirment:

High Performance , Full ESD protection for non-standard I/O:

支持的半导体厂工艺:

看不到附件

漏了ESD 两个附件:

1. BETTER IO/SOC PERFORMANCE AND ROBUSTNESS AT LOWER COST:

2. LOWER COST, HIGH VOLTAGE SOLUTION TO MEET SYSTEM LEVEL ESD/EOS REQUIREMENT

什么意思?

介绍了一家叫icsense的公司,在ESD方面很专业。

台湾的柯明道网页下有很多ESD的资料

挺有用的由PDF吗?

学习学习