模拟输入buffer的架构

时间:10-02

整理:3721RD

点击:

最近要做一个输入buffer,性能如下:

只有容性负载CL=34pF

电流不超过3mA

能在125ns以内建立稳定 稳定精度在5e-6以内

AVDD=5V

输入范围 AGND ~ AVDD-2V

感觉挺难做的,版上的各位大牛们,有没有什么推荐的电路?

还请各位多多指点哈

只有容性负载CL=34pF

电流不超过3mA

能在125ns以内建立稳定 稳定精度在5e-6以内

AVDD=5V

输入范围 AGND ~ AVDD-2V

感觉挺难做的,版上的各位大牛们,有没有什么推荐的电路?

还请各位多多指点哈

插播一条广告,如果贵公司需要FIB服务,可以联系我们。

本电路UBW很大,不过IQ也很大,应该不难,建议CASCODE 两级,自己调试下参数。

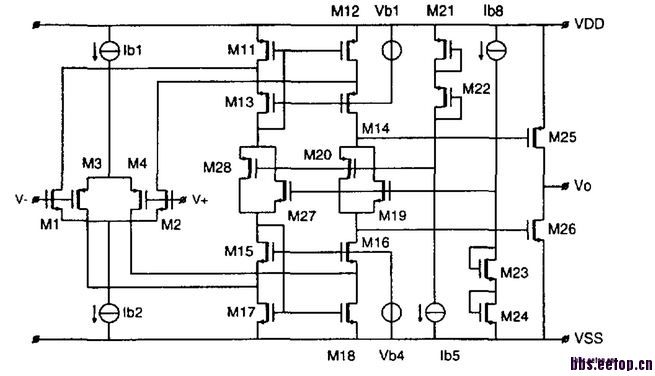

目前用的是下面的电路,但是问题是现在看来有两个问题:

1.负载电容比较大 要满足SR和带宽要求 补偿起来比较困难

2. 后面AB类管子尺寸如果尺寸很大,很难将output range的低值压到GND,甚至几十mv都很难。

VGND~VDD-2V,可以就用pmos输入啊,不用轨到轨的,补偿就是Miller补偿

嗯,现在问题:

1 如何在较低输入,比如vin=几十mV内,作为buffer,输出的精度在125ns时间内也能保持到需要的精度范围。

2 用到的就是米勒补偿,感觉补偿起来还是比较难。

直接开环的source/emmiter follower不知道可以不