关于仿真电路的搭建

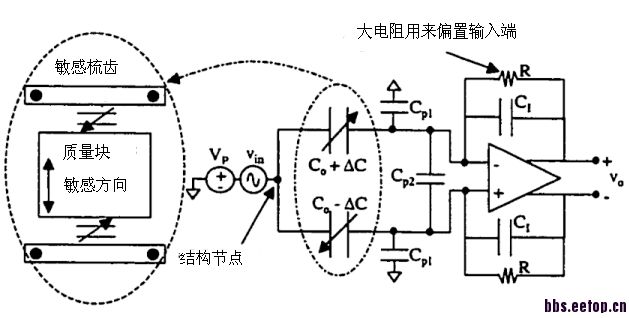

想请教一下,这个前端的差分电容在cadence里边怎么构造出来啊。求大神指教。多谢

是在cadence spectre下(Linux)

“C0 + delta C”“C0 - delta C ” 两者串起来接入输入端既可

谢谢

像小编求教:

导入verilog生成逻辑控制电路,但是有问题无法生成symbol,小女子不胜感激。

*W,DLNOHV: Unable to find an 'hdl.var' file to load in.

TOOL:

ncvlog

05.50-E115: Started on Apr 29, 2015 at 15:26:03 CST

ncvlog

-use5x

-ESCAPEDNAME

-work __nclib

-view module

-logfile ncvlog.log

-cdslib /tmp/ihdl_cdsliba2756_22756

-messages

-nostdout

-nocopyright

/home/dianke/ic5141/design/sar_logic.v

file: /home/dianke/ic5141/design/sar_logic.v

assign start=!en_! & en_reg;

|

ncvlog:

*E,EXPSMC (/home/dianke/ic5141/design/sar_logic.v,28|20): expecting a semicolon (';') [6.1(IEEE)].

begin

|

ncvlog:

*E,CSISYX (/home/dianke/ic5141/design/sar_logic.v,110|21): case item syntax error [9.5(IEEE)].

default:

|

ncvlog:

*E,NOTSTT (/home/dianke/ic5141/design/sar_logic.v,114|22): expecting a statement [9(IEEE)].

endcase

|

ncvlog:

*E,NOTSTT (/home/dianke/ic5141/design/sar_logic.v,119|21): expecting a statement [9(IEEE)].

module __nclib.sar_logic:module

errors: 4, warnings: 0

Total errors/warnings found outside modules and primitives:

errors: 0, warnings: 1

TOOL:

ncvlog

05.50-E115: Exiting on Apr 29, 2015 at 15:26:03 CST(total: 00:00:00)