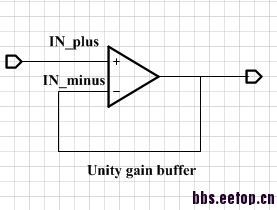

各位模拟大师,运放输入端作用,用在锁相环PLL,消除电荷共享的单位增益缓冲器

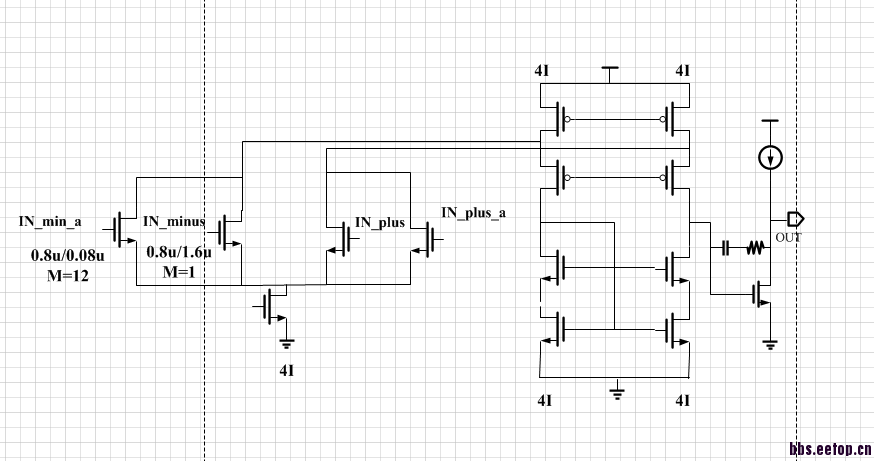

上图就是单位增益缓冲器结构示意图,输入端in_plus和in_minus管子尺寸是很小的倒比管,0.8u/1.6u,并且m=1,奇怪吧,输入差分对管怎么这样的尺寸呢?各位请发表高见,如果这里只是小奇怪的话,更奇怪的是,与差分输入对管并联的in_plus_a和in_minus_a管,首先尺寸很大,0.8u/0.08u,m=12,是输入对管宽长比的240倍,而且in_plus_a和in_minus_a是in_plus和in_minus level shift 一个VGS来的,在正常工作条件下,是不会开启的见下图,

,小弟百思不得其解:这个level shift 电压从到差分输入端的作用是什么,因为正常工作条件下,level shift 之后的电压会让0.8u/0.08u m=12的管子在亚阈值区,这是在PLL中消除电荷共享所用到的unity gain buffer,也经过多次流片验证 ,请各位模拟大神们,发表高见,小弟在此谢过了!

,小弟百思不得其解:这个level shift 电压从到差分输入端的作用是什么,因为正常工作条件下,level shift 之后的电压会让0.8u/0.08u m=12的管子在亚阈值区,这是在PLL中消除电荷共享所用到的unity gain buffer,也经过多次流片验证 ,请各位模拟大神们,发表高见,小弟在此谢过了!

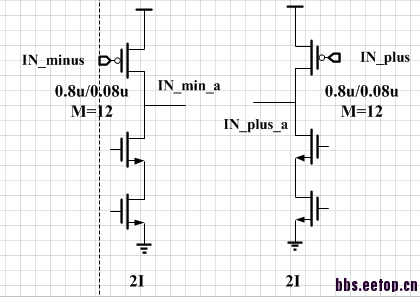

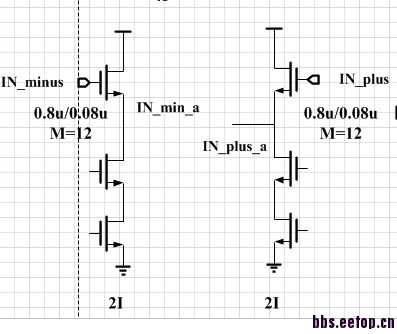

而且in_plus_a和in_minus_a是in_plus和in_minus level shift 一个VGS来的

==> 看着不像是level shift一个VGS,可以再详细描述一下in_plus_a / in_minus_a 的产生吗

seeing...

运放里面也有MOS

看一看

不好意思,手误,应该是NMOS source follower 见下图,

level shift 一个Vgs ,由于NMOS管比较大,所以level shift 大约一个Vth,导致正常工作条件下,in_plus_a和in_minus_a使 与差分对输入管并联的大管子进入亚阈值区,感觉没什么用,不知道大家有没有见过这种电路,作用是什么?

感觉是考虑放大器摆率,或者输入钳位之类的作用,请求各位模拟大神露面,解开谜底啊

!

再次置顶,望有人解答

继续顶啊

继续顶啊

麻烦告知一下input swing和common mode多少

input swing大约在0.3v,common mode 0.9v

麻烦告知一下input swing和common mode多少

source buffer 就做level shift 阿,只是shift造成下級即進入subthreshold 是不太好的

怕 DC 一跑掉OP就關掉了,chargesharing功能就沒用了

source buffer 就做level shift 阿,只是shift造成下級即進入subthreshold 是不太好的

怕 DC 一跑掉OP就關掉了,chargesharing功能就沒用了

感谢兄台答复,还有些疑问,请兄弟明示,

1)为什么输入对管input pair1 的尺寸是倒比的,尺寸很小,0.8u/1.6u,m=1,也就是说正常工作电压范围内的输入管gm很小(偏置电流一定的)?

2)为什么输入端电压level shift 之后,再送会到输入端的input pair 2 尺寸非常大(level shift 的偏置电流和input pair1的相等),0.8u/0.08u,m=12,而在正常工作时,这个input pair 是进入亚阈值区的,管子根本不会开启,DC Vgs大约在0.2v或者0.3v之间(Vth=0.6-0.7v),也就是说目的就让这个input pair2在正常工作电压范围时不起作用?

3)“怕 DC 一跑掉OP就關掉了,chargesharing功能就沒用了” 这个的意思,我也考虑过了,有可能输入端DC电压突然跳的太高,那么此时OP当然就不起charge sharing elnimate 作用了,level shift 之后,input pair2 就会在正常工作范围内,OP就可以正常工作对吧?举个例子,input pair 1 和level shift的偏置电流相等,比如:in-plus DC突然跳至2.3v(高压电源3.3v),那么level shift 之后in-plus-a 的DC 大约在1.8v左右,均超过1.2v低压输入对管的范围,请大家发表高见,跪求大侠解答?

图好乱······没看懂··