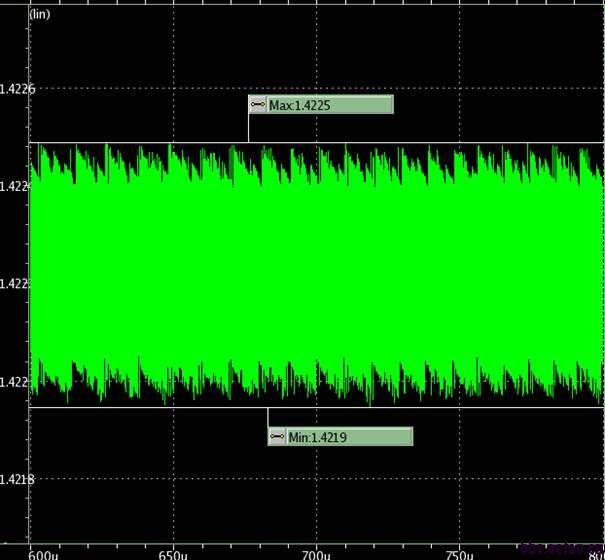

PLL仿真Vcn存在一个周期性变化,求助不知道这个周期性变化是怎么来的。谢谢

时间:10-02

整理:3721RD

点击:

如图,VCO振荡频率是1.6G,refclk是24M

SSC没开,好像也不是DSM引入的(这点我不确定),不知道这个周期性变化是哪来的?

实在是想不出来哪里引入的。

希望大家能给个参考我去check,谢谢

Hi xipan:

Is it pre-sim result?

Could you show the up, down and the output signal of divider?

Thanks.

mpig

这应该是DDSM的量化噪声

似乎你的小数分频约等于

100k/24M=0.0042