请教S/H电路中开关问题

可是一用栅自举开关,输出波形根本就乱(应该说根本就是乱波)。

我以为栅自举开关做得不好,我就再全部换上理想开关,把保持相的开关换成了CMOS开关(这开关我仿真了它的输出电阻性能,保持它的电阻在250欧左右),一般资料上说,保持相的开关可能用CMOS开关,因为自举开关占面积大,一般就在采样相做开关。其它的开关都是理相开关。大家说说为什么会这样子。本人只换了一对理想开关。

我想可能是你在理想的时候clk信号是non-overlap的, 但是用了boot-strap开关后,由于boot-strap产生的延时,

导致clk信号不是non-overlap了,你先看看是不是这个方面没做好。

我想,可能不是这个原因吧(不过,我还是去电路中检查一下)。

因为我把所有开关都用理想,就是把保持相的开关换成CMOS开关,输出信号还是没有波形。而所有的时钟都没有变。一般来讲,如果CMOS宽长比够的话,信号通过CMOS开关的延时非常小的,可以忽略不计。

我看了很多开关电路书,都没有讲什么特别的东西。一般来讲,开关主要注意的沟道注入,时钟馈通,还能导通电阻和电容所构成的带宽问题。而现在为什么会出现这种问题,想不明白!

别人都说采样保持电路主要是运放做得好不好,会不会问题出现在运放上呢,可是运放仿真结果都很好。而且用理想开关仿真的时候,都可以出波形,证明运放是可以工作的。

晕晕!

我说的延时不是指开关导通的延时,而是指clk信号进去到boot-strap信号产生这个时间。

你只要保证这个boot-strap信号和hold信号是non-overlap了,应该可以的,还有那个bottom-plate sampling信号。

运放不是太大的问题。

小编,你说的意思,是底极采样时,所要注意的时钟问题?

boot-strap信号指的是什么,能说成中文吗?不然,我没有理解它所表达的意思!

额....

反正就是说,只要你把开关的控制信号的时序做好了,开关的导通电阻足够小了,那么肯定可以出来你要的波形。

运放不是大问题。

boot-strap switch就是指自举开关啊,他的gate控制信号从clk过来是会有延时的。

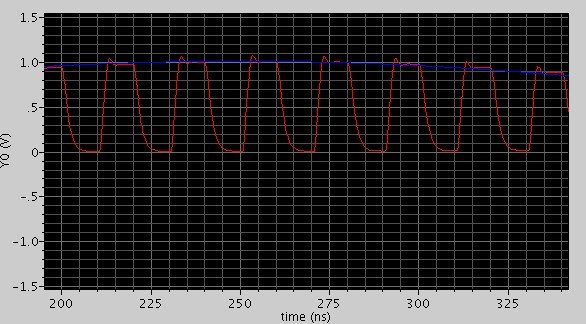

调试了一下,现在仿真结果是好多了。不过,离目标还是有好大的差距,波形不是很好。

就是在减少开关的导通电阻时,怎么去考虑沟通注入效应。在减少开关导通电阻时,肯定要增大W,沟道注入效应会更加明显。有什么方法去测沟道注入效应?

你说的时钟问题也必须得考虑,因为在电路中,有些开关用了自举开关,有些用的是CMOS开关,在信号传输过程中肯定会有延时,可能对输出影响还是比较大的。

用了cmos switch,charge injection应该会比较小的,而且由于cmos switch 是开关并联,所以w/l不会太大了。

怎么测这个charge injection我是不了解的。你上面所提到的问题,我通过电路仿真后,发现延迟还是比较严重的,达到0.2ns左右,就是说时钟clk和gate控制信号存在0.2ns延迟,那采样保持电路中其它时钟信号和clk信号是通过同一电路产生的,也就是说gate控制信号和其它时钟存在不正确的时序了,你是怎么解决这种问题的,能否给点建议,谢谢!

用inverter产生延时来匹配啊.

对于采样开关来说,最终还是要以其谐波失真做衡量。如果是查分结构,一般需要关注其三次谐波THD3的影响