积分器输出保持时间问题

时间:10-02

整理:3721RD

点击:

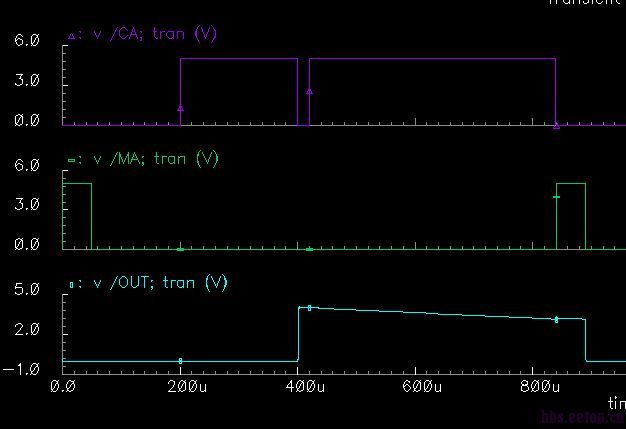

如图所示,1C是积分相,1D是保持输出相,波形图如下所示:

CA为高的时候积分,MA为高的时候保持输出,从仿真看输出只能保持10us左右就开始往下掉,这是什么原因?

漏电了

可以预期。晶体管,电容器泄漏的费用。

有什么办法优化吗?

通过电路防止电容漏电路径。(像CMOS开关漏电或CMOS晶体管的栅极漏...)。如果电容本身的泄漏不是使用的电容增加其极板之间距离较大,这意味着不同类型的电容器,但大小。

非常感谢,一般是怎么做的呢?

问题是,这些东西都是电路实现依赖。我不知道你的电路。

大概就是这个样子,求解释啊

看起来像你的交换机是理想的,他们不是晶体管级的组件。什么是你的“在关机状态下”值开关在你的理想的“R”的模式?什么是你的电容值?你检查你的电容漏电开关关“R”?如果这不是永远的问题,那么什么是你的运算放大器输入漏?如果你有一个运算放大器由晶体管是一个真正的电路中,如果您使用的是亚微米工艺改进的栅极泄漏是艰巨的,需要在设计中要慎重考虑。

试图找出其中电容器充电泄漏。由于这是一个小的电路,很容易把零伏理想电压源上的每个电路分支,并测量这些分支的电流,以便确定哪里是泄漏。

祝好运!如果你试图去探索尽可能多的正在发生的事情在你的模拟和熟悉的最好的。

冒昧问下,这是英语翻译过来的吗?有些句子我看起来有点吃力

找到问题了,从开关漏电,我把开关宽MOS管调成倒宽敞比,问题就解决了

我很高兴。良好的工作!