incremental delta sigma 第二阶积分器输出结果不对求助(有图)

时间:10-02

整理:3721RD

点击:

rt

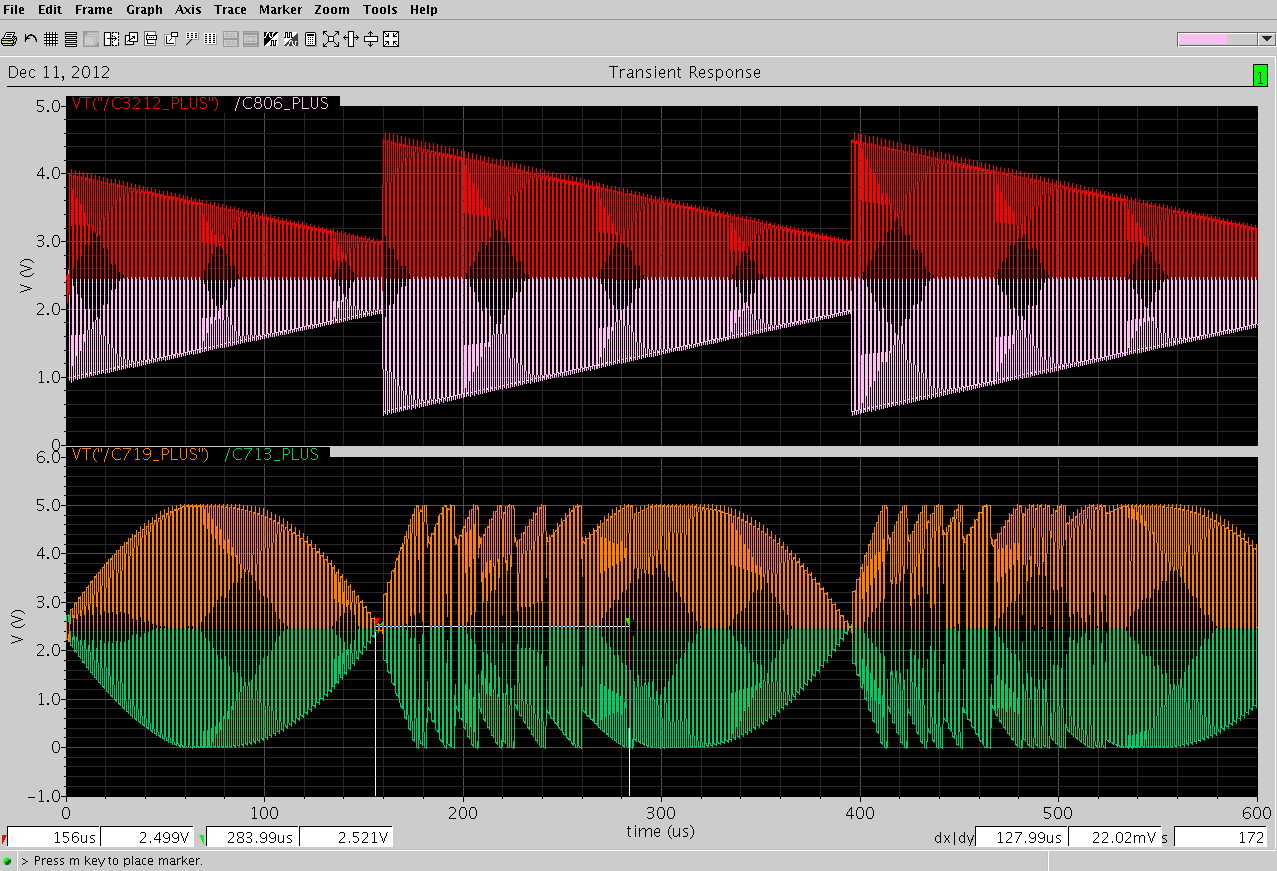

仿真的是一个二阶的incremental delta-sigma ADC,用来测量直流电压。

输入信号为5.2V的直流电压,上面的图为第一级积分器的输出,下面为第二级的积分器输出。

理论上的输入信号上限为5.4V,但是现在5.2V的时候第二级积分器的输出就开始出现了"截峰"(不知这么叫对不对)

电容比例第一级为1:4,第二级还是1:4。

不知道为什么第二级的输出在趋向于截峰(150u~300u)的时候为什么还会突然往下掉,求高手指点!

下面这个图是输入为4.5V时的波形

这种情况,一般都是开关时序不对或者信号相位不对的原因。

建议先用VerilogA模型仿真,确认时序对了之后再用实际电路代替,不然仿真很慢,不好排错。

输入小于5V的时候,两个积分器输出都不会发生截峰的情况,所以时序应该没问题

你的量化器的输出不正常吧,长高长低?

第二级输出每次到达中线的时候就翻转一个时钟周期,然后再恢复高

木有人见过这种情况吗?

电路饱和掉了吧,检查下直流点吧

确实是电路饱和了,电容有较大偏差, 已经解决了,谢谢啊!

高手高手~~厉害厉害~~

just learning !

您好,请问你最后是怎么调好的?我在看一个2-1结构的,第三级积分器输出也是削顶了,不知道调什么