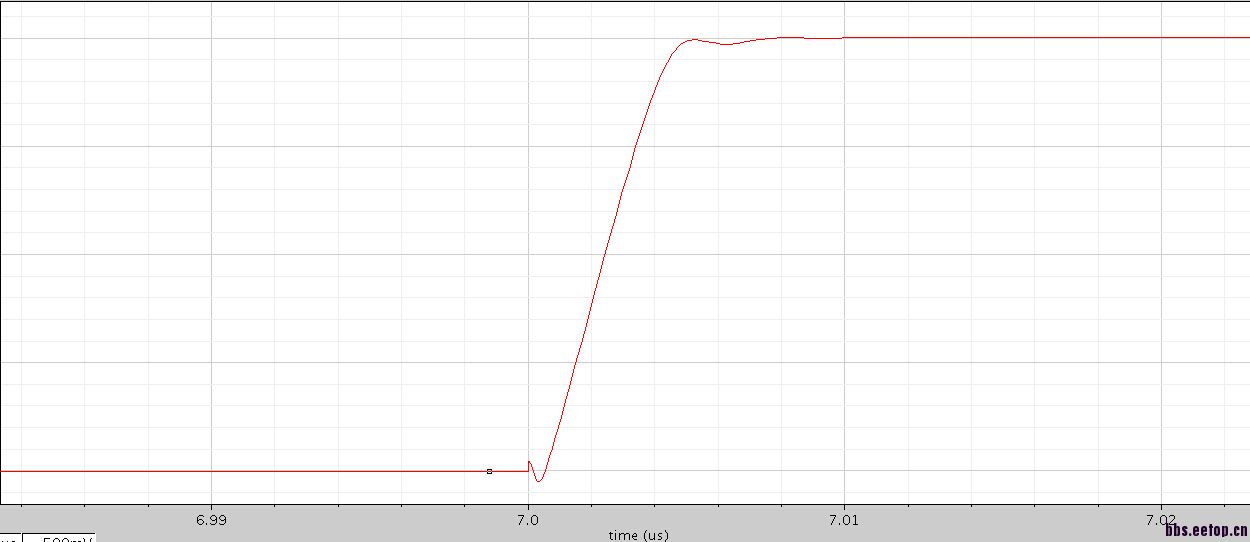

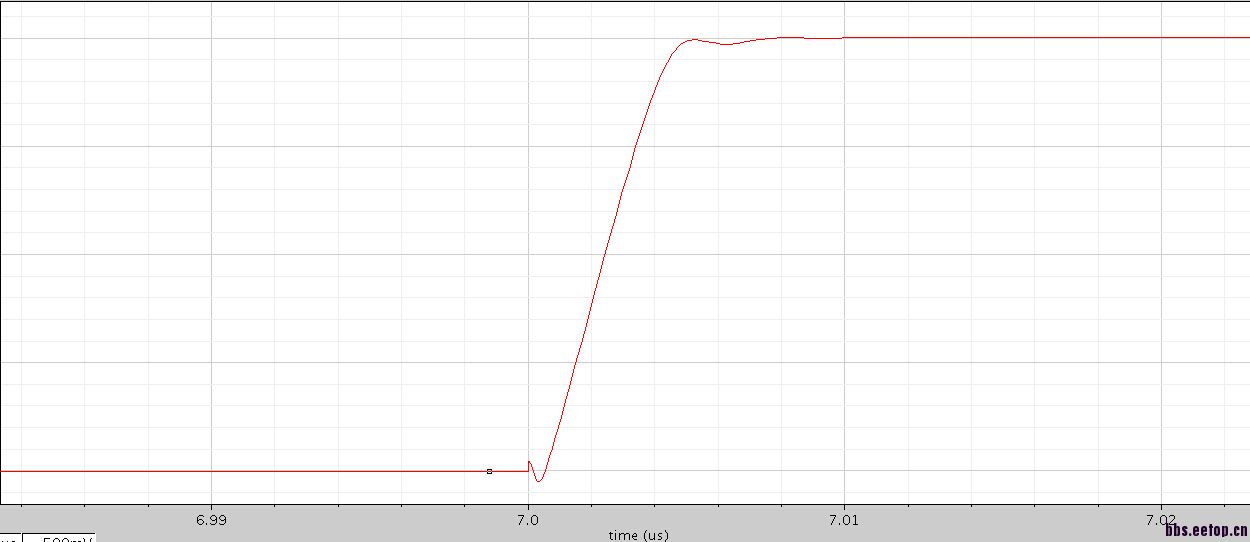

仿SR的时候底部有过冲

时间:10-02

整理:3721RD

点击:

各位大神,小弟在仿运放SR的时候,加的500-900mV的阶跃,结果底部出现过冲,请问有谁知道这是为什么吗?难道是PM不够?

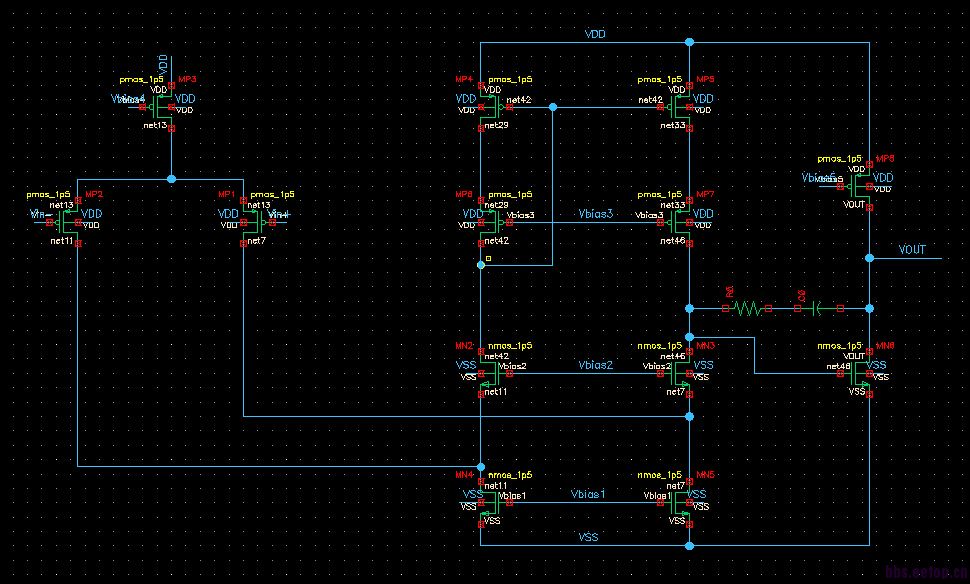

你好,我的电路图就是普通的二级折叠共源共栅结构

比如说零点

零点?零点怎样影响的呢?

能把电路图传上来吗?估计可能是寄生电容造成的,需要看具体电路,才能判断问题出在哪里了?

你好,我的电路图就是普通的二级折叠共源共栅结构

这是输出MOS M6的寄生COX造成的,在电路正常工作之前,各支路分压VDD。比如第一级输出分压值为10mV,第二级输出分压为5mV,N管M6栅电容两端压差为-5mV。在电路导通的瞬间,第一级先导通,输出为零,第二级正常建立需要一段时间,在此之前,由于电容电荷不能突变,需要维持-5mV的压差,因此输出会在这瞬间建立一个-5mV的电压,类似于pump产生负压。

纯属个人愚见,哈哈。你可以调整M6的L,让它大些,这样子第二级分压就会大于第一级,按理说是不会出现负压的,验证一下。