请教:关于传输门的veriloga的建模问题

所以想请教:如何对传输门(或模拟开关)进行veriloga建模,

望高手不吝指点,谢谢

汗 求助还要卖钱的?什么世道…

谢谢小编了

有没有人回答啊

我也面临同样的问题。如果知道传输方向还好,有使能信号就让输出等于输入。但是好多情况是输入输出不分的,有时候从左到右,有时候从右到左,这种情况就不知道怎么编了。目前是用数模混仿来搞,不知有没有高手解答一下怎么用verilog实现输入输出不定的传输门。

A. Switch

A voltage-controlled resistor represents a basic switch characteristic. The resistance between nodes 2 and 0 varies linearly, from 10 meg to 1 m ohms, when voltage across nodes 1 and 0 varies between 0 and 1 volt. The resistance remains at 10 meg when below the lower voltage limit, and at 1 m ohms when above the upper voltage limit.

Gswitch 2 0 VCR PWL(1) 1 0 0v,10meg 1v,1m

B. Switch-Level MOSFET

To model a switch level n-channel MOSFET, use the N-piecewise linear resistance switch. The resistance value does not change when you switch the d and s node positions.

Gnmos d s VCR NPWL(1) g s LEVEL=1 0.4v,150g 1v,10meg 2v,50k 3v,4k 5v,2k

请问你写的gswitch的语句是在建模的时候为什么提示语法错误?压控电阻的veriloga模型hspice不认么,或者说需要用另外的语句来描述压控电阻才能用?

急求你的解答,谢谢~

请问gnoms受控源中的控制电压具体指的是什么电压,或者是那两个电极之间的电压

参考您的第一个hspice开关模型,写了个hspice下的开环Buck仿真:下面为代码:

****

Gswitch drain source VCR PWL(1) gate gnd 0v,10meg 5v,1m

vdd drain gnd 10

vvc gate gndpwl 0 0 0.99u 0 1u 6 1.9u 6 2u 0 r 0

L1 source vout 20u

C1 vout gnd 47u

RL vout gnd 5

D1 gnd source powerdiode

.model powerdiode D

+IS=1m

.ic v(gate)=0

.tran 1n 1m uic

.print i(*) v(*)

.end

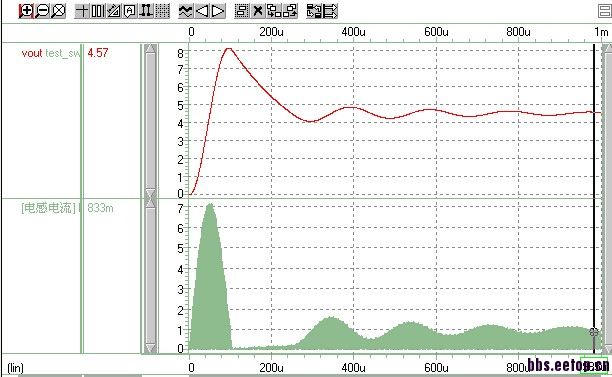

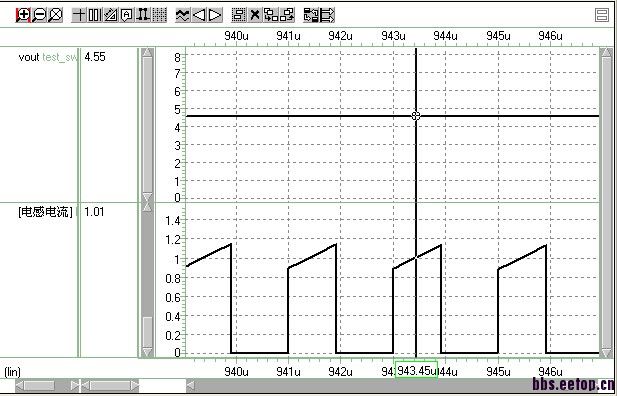

下面是仿真结果