关于Matlab仿真DAC的INL和DNL的问题

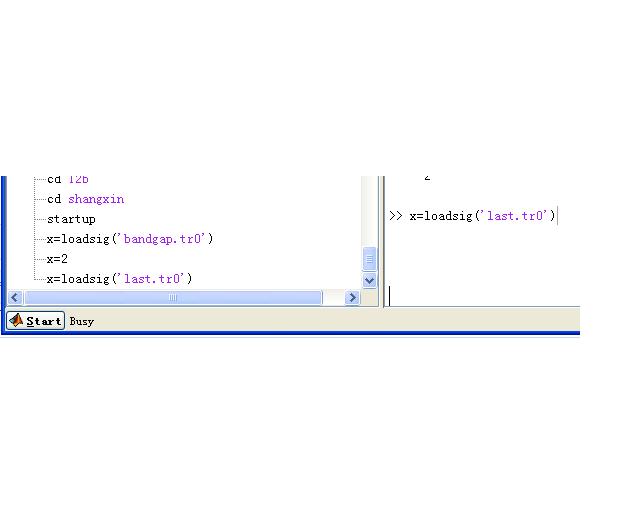

利用hspice toolbox在Matlab中 使用x=loadsig('last.tr0')last.tr0是我的仿真文件名

可是从早上10点到现在为止 Matlab始终是没有输出结果 左下角显示busy。

所以我想知道 大家怎么把这么大的数据量输入给Matlab的 Matlab能处理这么大(2-3G)左右的输入数据量吗?

不胜感谢!!

你这样做有点问题,首先,.tran的时候没有必要所有变量都看,所以你的文件很大,另外你的仿真结果要做什么处理的?静态还是动态,还有你的输出信号往Matlab里导的时候,直接取点是不对的,最好用并行输出,不然算出来的结果是没意义的。祝你成功,小显仔

感谢小编

我在做.tran的时候

用的是.tran 4n 16384n

然后就是 print i(rr1)

如果我要减少输出量 该怎么写呢?

另外在生成了数据量很大的tr0文件后 怎么将其中的点尽量少的导入到matlab呢

我刚开始使用loadsig函数 发现不行

后来 我看在list文件中 有我的print出来的数据 于是我把数据放入了txt里面 后来用load语句导进去的

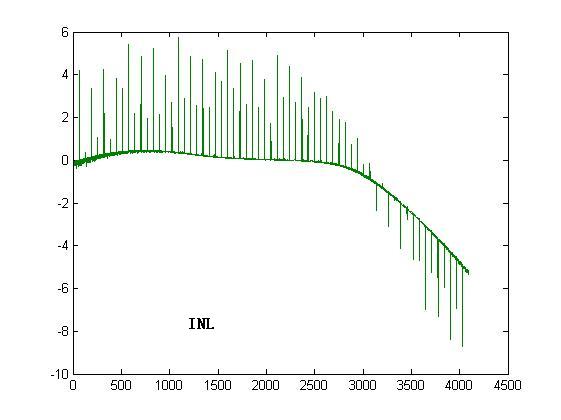

还有一个关于INL的仿真中出现的问题

在仿真的波形中 我发现随着输入数据从全0到全1尤其到后面的时候 INL呈现出增大的趋势

这是什么原因呢 难道是所谓的增益偏差吗?

谢谢了

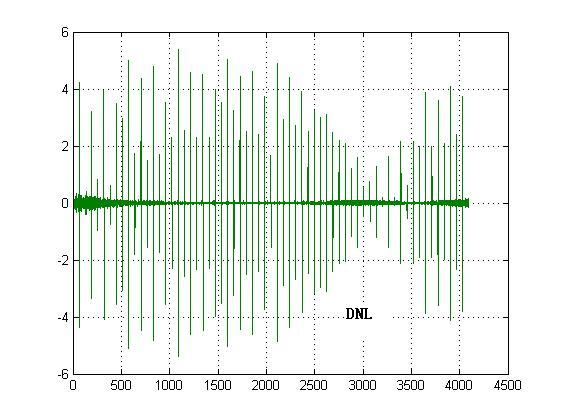

上面两个图是我把输入从 全0 逐渐变成全1的时候clock的频率为250Mhz的时候仿真的 效果非常不好

当我把clock频率降低以后

波形得到改善 所以我想知道

是不是仿真INL DNL这些静态数据的时候 不需要那么高的频率了

只有在仿真SFDR的时候才要高频clock呢?

1. No. CLOCK still the same

2. Now your simulation only show the DNL/INL due to systematic errors. It will be much worse if having mismatch data.感谢你的回答

在仿真的时候 数据量很大 怎么能较少仿真时间呢

我的时钟周期是5n

然后我在瞬态仿真的时候写的是.tran 5n 102400n

感觉不对 恳请指教eetop还得好好学习啊。

就没有牛人出来指导一下么,呵呵

一看就是牛人回帖,关于这个东西你能不能仔细讲解一下或者推荐一个文档,呵呵

感觉matlab处理是个很好的方法

其实我的看法和很多人一样,没有mismatch的信息,这个DNL和INL的仿真没有什么意义

因为这个仿真时间确实很长,仿真的时间由每个LSB至少4个点(有人说是10个点)决定

这样知道你的bit数,仿真时间也就定下来了

还是那句话,这个仿真没有意义,如果有mismatch信息的话,得做monte-carlo仿真,这个仿真时间太长,数据太大感谢楼上的回答 那么只能仿真SFDR看看性能啦

或者后仿真的时候可以看看 不过估计时间会更长路过,学写了

你的INL在两端为啥不是0呢?

dingdingding ding

小编怎么仿真的?

学习下,呵呵

学习了

i am agree that it would be better to take mismatch into account, but i still have no idea about doing that.

没有仿真过INL DNL 一直想仿 可是不会~悲剧 马上毕业了 做了一个DAC 可是在流片前 这个都没有仿出来 悲催啊~

matlab还是要好好学啊

好诡异,@perfect_ic 哪去了?为什么我看不到

路过,学写了

小编,能给份matlab程序吗?怎么做得啊?

還得好好學習啊。