求大神解答?VCO测试结果比后仿差很多

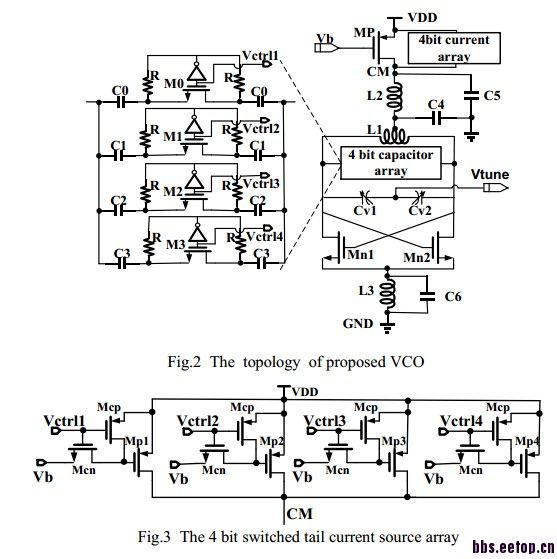

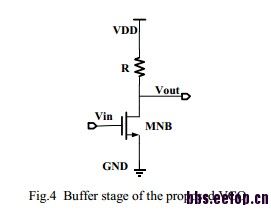

VCO核心电路图:缓冲电路:

后仿tt工艺角,输出频率范围4.5-6.6GHz,相位噪声-107dBC/Hz至-117dBC/Hz。

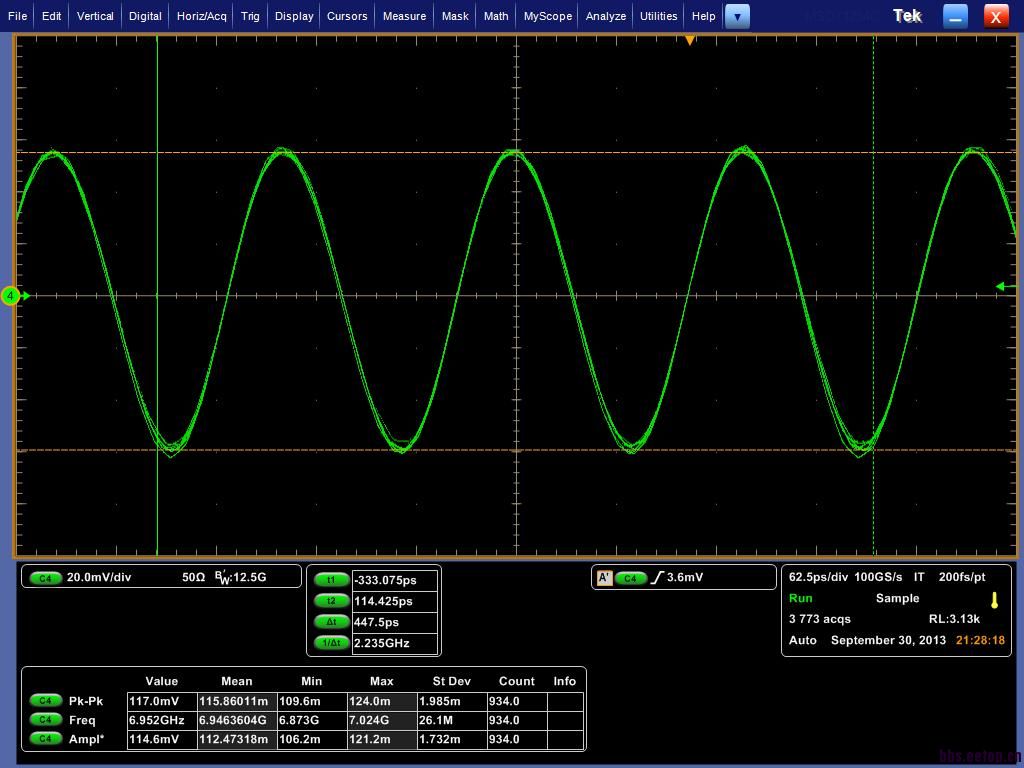

测试结果,输出频率4.3-6.9GHz,相位噪声-70dBC/Hz至-80dBC/Hz。

为什么测试频率比后仿的频率更高?后仿中没有考虑的寄生电感和电容怎么没有起作用?相位噪声为什么这么差?现在无法确定主要原因是测试方法还是电路设计或者版图上的问题。此外,测试时只在Vtune端外接滤波电容。请大家畅所欲言,不管是测试方法还是电路设计上的问题。谢谢~

tuning range 和 其他参数都是trade off的。 你tuning range 比 spec大出一些,说明你的实际有效电感值要比理论值小。L/C决定phase noise的表现,所以你的pn变差。L3 C6是否准确在2倍频共振也需要考虑。增加电感面积,增加switch开启电压。因为可能出现问题的地方太多了,只能说一点个人意见。

频谱仪测的还是信号源分析仪测的相噪?

simulation tt 不表示 流片會在 tt .

一般是 tt/ss/ff/sf/fs5 corner sim ..如果今天你其中一個 simulation 真的有跑到 6.9Ghz ..

會不會如此 ?

能贴一张phase noise的图片吗? 从来没见过这么差PN的VCO

在不关于VCO讨论 qq联系好不?

谢谢!L/C决定phase noise性能怎么理解?L越大相位噪声性能越好?另外,二次谐振滤波只在某些频点上效果比较好,但是测试结果所有频率上相位噪声性能都比较差,难道流片出来二次谐振滤波网络不起作用?

频谱仪Agilent 4440A。这两个仪器测试结果差别很大吗?

仿了一下,ff,temp=27. 频率范围4.7~6.9GHz,相位噪声最差时也有-110dBC/Hz@1MHz。很纳闷,测试结果咋会这么差?测试方法还是电路/版图出现的问题可能性更大?

等过几天,图还在仪器里没有拷出来。频偏1MHz到3.5MHz之间,相位曲线会往上翘出现一个小尖峰,可能是什么原因?后仿时相位曲线没有出现尖峰,而是正常的-20dB/dec这样往下降。

你的QQ是多少?欢迎讨论。

频谱仪测的相噪好像得转化一下才是真实的相噪,以前在书上见到过,不过式子忘了。

小的上突是spur,5052b是可以关掉的。你的读数是avg之后的吗? input freq range是否合适?

测到的dbc-10log rbw-修正因子,

修正因子一般1-2db

不是很明白,Agilent 4440A里的Phase Noise功能可以直接读出相位噪声(单位是dBC/Hz),这个还需要利用公式另外算相位噪声吗?

我的这个应该不是spur,因为VCO是单独送出去流片的,而且相位噪声曲线拱起的部分频率范围比较宽。读书是AVG之后的。请问 input freq range取多少合适?

L/C 越大,phase noise性能越好。这个结论在ABIDI,HAJIMIRI等大神的文章里都有体现。如果你没有耐心看文章学习,直观的说:

之所以是L远大于C对噪声好,是因为tank的Loss主要由L决定(QL远小于QC)。所以,R_parallel=Qtank * squr_root(L/C)。对于一定的工作频率和QL,max(QL,max = Qtank,max),为了增加R_para,只能提高L/C。

为何要增加R_para? 因为在一定DC电流的条件下,增加R_para是提高carrier摆幅的最直接方法(不考虑class-C)。而SWING与phase noise 直接反相关。

所以增加L/C对于pn有利。显而易见,L乘以C是固定的,而C越小,tuning range就越小。这就是我说trade-off的意思。希望能帮到你!

Reference:

T. Lee and A. Hajimiri, “Oscillator phase noise: a tutorial,” IEEE J. Solid-State Circuits, vol. 35, no. 3, pp. 326–336, Mar. 2000.

M. Tiebout, “Low-power low-phase-noise differential tuned quadrature VCO design in standard CMOS,” IEEE J. Solid-State Circuits, vol. 36, no. 7, pp. 1018–1024, Jul. 2001.

至于第二个问题,关于noise filtering。你必须让你的共模点谐振在2倍频。因为那个点寄生电容很多,你最好引出来测一下那一点的频率。否则很可能仿真结果很好,因为滤掉了很多噪声;而流出来很差。

Good luck!

非常感谢你的耐心回复!L/C越大,同样DC电流下的摆幅更大,能够提高相位噪声性能。然而,L越大时,谐振腔的等效并联电阻也会更大,从而增大了谐振腔的电阻热噪声,是否意味着谐振腔对VCO贡献更多的相位噪声呢?

看过ABIDI和HAJIMI的文章,感觉里面有很多tradeoff,但是实际优化VCO相位噪声性能时不知道从哪个方面优化比较好。

二次谐振滤波网络如果要引出测试引脚,是否与实际工作时的VCO工作状态不一样?毕竟PAD上会有寄生电容/电感/电阻。

小弟对VCO的认识比较肤浅,还请多多指教~

你说的没错,但是这就和增加输入管子是跨导能减小噪声一样。注意,噪声的功率和跨导正比,而信号功率确和跨导平方正比。所以增加跨导在一定范围内有net gain. VCO也一样,噪声的增长慢于摆幅的增长,去查查LEESON MODEL 表达式便知。这种定量的东西不能只靠简单的直觉了,是我没讲清楚。

噪声模型和产生机制方面的paper比较多,看得我有点晕了。

只看ABIDI就对了

如果直接有phase noise plot的功能,就不需要了,把这些都考虑进去了

L/C的比值同时也限制了tuning range,通常用capacitor tuning,C越小tuning 越难做,而且片上的L也有自己的self-resonance, L越大,Q越低,所以都需要trade-off.

R越大,引入的thermal noise 确实会增加,但是coversion gain很大大降低,等效来说,phase noise性能是变好的。

input freq range 要很好的cover你输入信号的freq,不要太close to the edge。

来个phase noise的picture看看,分析起来容易多了

根据经验,后仿的结果和测试的结果不该相差这么大,我认为。

你的情况的原因可能有:1,测试仪器坏了(这个真的可以有),先确认仪器坏没坏;2,输出功率太小,我以前测试的时候把功率调的非常小的时候相噪恶化很严重,几十dBc/Hz的降。

应该不是你设计的问题,看看PCB的输出端50欧姆匹配了没?输出功率是不是很小等。

VCO在片测试,输出缓冲没有做50欧姆的匹配,经过巴伦接到频谱仪后功率-9dBm。设备应该没坏,正在换一块芯片测试。

频谱仪复制图片太麻烦,还没有复制出来。现在只有示波器的图。请帮忙分析分析~多谢了

直接看波形是没有任何用的

用你的手机拍个相片,上传上来就行了,为啥要复制出来? 这里又不需要高清

我不是很明白一个4~7G的VCO为什么要在片测试?有什么特殊的要求?直接上PCB做COB然后测试不是很方便,测输出很方便然后控制也方便啊。