请教Serdes TX眼图如何开的问题

以下红色文字是2楼@wuzl423的原话

不知道你说的TX设计包含哪些,一般来说只包含:Serializer 和 driver。这两个地方其实都比较简单。

Serializer主要看看timing,因为这部分一般都是采用standcell完成的;

Driver部分要看你采用什么结构,是CML还是电压形式,主要看下:输出阻抗---阻抗匹配要求;输出幅度;眼图,如果是理想负载,时钟也是理想的,jitter应该很小。

但是其实TX应该考究的还有:(1)时钟质量,一般是PLL的设计决定了,所以要考虑PLL输出时钟的PhaseNoise,如果是半速方式的,还要考究时钟的占空比;(2)封装和传输线影响,因为很多Serdes对传输线是有要求的,需要远端测试指标。此时就要考虑一些预加重技术了来消除ISI的影响,具体预加重方式要根据负载来设计了。

我的问题来了:

封装拉线和PCB走线通常会有寄生,导致ISI,对于电压或者CML的driver,data速度太慢,眼开太小

开预加重作用不大,通常大家都会如何解决该问题?

是对封装和PCB布线有何要求,或是Driver设计有什么要注意的

谢谢各位啦

走了信道之后眼睛闭合,不过接收端不是也有均衡么?眼就开了吧

你知道所用PCB走线造成多大高频损失吗?预加重大小合适可以补偿传输损失,帮助眼图打开,预加重过多会反过来会增加ISI而损害眼图---过犹不及!

谢谢,但是发射端有mask限制

多谢回复

pcb的没概念,没抽过参数,可以讲解一下吗,我要仿真的话应该怎么加?

另外就是封装线的影响,需要注意哪方面?

因我仿真只加了封装线模型和3pf左右的负载电容,发现眼图开角角度太小,要加很大的预加重勉强打开,isi还是严重

对了,是CML 3.6g信号,片外电阻负载

再请你指点了,感激不尽

可以简单测几个不同频率信号衰减的量,做个简单模型,用该模型仿真看看加多少预加重改善比较好。如果预加重设计的步长够细也可以逐渐改变看看趋势,或许可以找到“优化”设置。总而言之,缺多少补多少,补合适受益,补不合适受害。具体情况具体分析,想法搞清楚实际情形是第一步而且必不可少,否则谈其它都是空中楼阁。

如果预先不知实际情况,有无经验值留多少预加重?以防到时加重不够

这两天追这个问题,追到了信号完整性,说封装键合线和高速pcb是设计的关键

作为设计者,只能留预加重的设计吗,同样的产品碰到不同实际环境要开不同预加重?

我们还可以做什么?比如对封装和pcb提要求?

刚接触这块,很多问题没整明白,还请再指教

感谢关注

电容越小是没问题,问题是碰到重负载就有问题

单纯的封装线 加起来1pF都不一定会到的!

高速 都是 小型化,扁平化封装

感谢ljj老兄关注

负载小没有问题,但我感觉还是要考虑最坏情形的发生

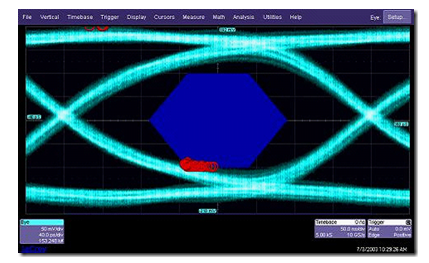

就像附图(从网上搜的图)这张眼图,开角很小,假设上升或者下降时间再慢点,就算数据抖动量再小,还是有可能碰到mask

对这种开角很小的眼睛,是否有办法让它再睁大点

主要还是对封装线寄生/PCB差分走线寄生这些不make sense而没想明白,希望高手再指点

封装参数估计不能太随意,不然你要白白增加功耗。

寄生Cap大了,自然要加大Tx的输出电流

好的,多谢啦

预加重只是为了补偿PCB/package信号损失,还是标准有预加重要求?

对信道做脉冲响应分析,再根据得到的结果选择TX FFE的tap种类,数量和权重。

seeing

通常接收端會加等化器, 所以只要不要太差都沒有問題.