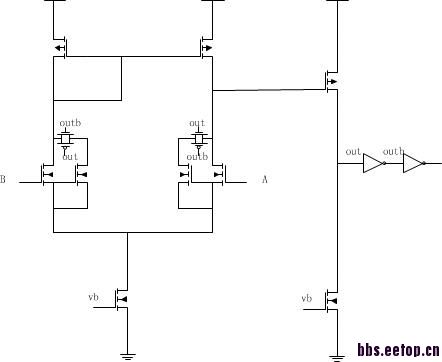

差分对不匹配的迟滞比较器

时间:10-02

整理:3721RD

点击:

做了一个迟滞电压为150mV的比较器,采用差分对不匹配的方法,但书上和网上都没看到这种结构。各位大神指点一下,看看有什么问题么。

做了一个迟滞电压为150mV的比较器,采用差分对不匹配的方法,但书上和网上都没看到这种结构。各位大神指点一下,看看有什么问题么。

看不到参数

A端口差分NMOS管的个数比为5比1,根据所需的迟滞电压设置的,B端口也是一样的结构

A端口差分NMOS管和迟滞NMOS管的个数比是5比1,B端口结构和A端口一样

可能控制栅极会鲁一些,你这个结构最差情况下传输门可能工作不正常

简单看了一下这个结构确实是可以迟滞的啊,比如:让B端固定在一个电位,A端电位从一个很高电平往下降,刚开始的时候Vout=1,Voutb=0,这时A管的传输门打开,在A侧Id是B侧的数倍,当A电位降到与B电位相等时,如果没有传输门的存在AB两边对称,在运放开环增益比较高的情况下应该立刻改变输出状态,但是由于传输门导致两边静态电流不对称,因此A侧栅端电位需要降低到更低以使两侧电流相等来使输出状态跳变,这个更低的A侧栅电位就越过了B侧栅电位,因此产生了迟滞。

具体迟滞窗口的大小和响应速度需要仔细的仿真。

你所指的极差情况是指什么情况呢

当响应达到摆率的时候这种结构应该和一般的两级比较器一样,响应只由偏置电流和结点电容决定,是吧?

学习了

用差分管和迟滞管的比例调节迟滞区间,有什么问题?

是的

差分对的B的drain端电压假设1V,假设你用的vth=0.7左右的管子,假设电源电压1.8,此时开关管基本打不开,电阻有几十兆,那么你那路迟滞就没用了

为啥两边都要加迟滞管?只在一边加也不错啊,既可以获得一定的迟滞,也可以有一个准确的翻转点。求解释!

嗯,你说有很在道理,在低电源下这种方案确实会出现问题。不过现在是5V应用,一般最低电压会保证在3.5V左右

只加一边的话只有单边迟滞啊

是的,但单边迟滞为何不可?还是没懂。

应用要求要双边迟滞哈