LDO设计高手来帮帮忙看看咋回事哦

下面是其结构:

;

; ;

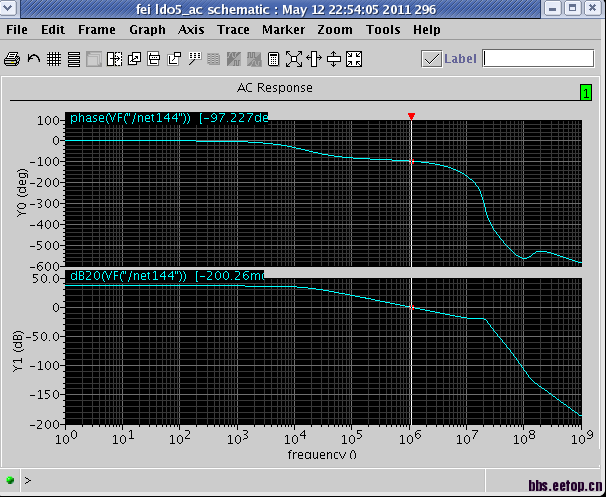

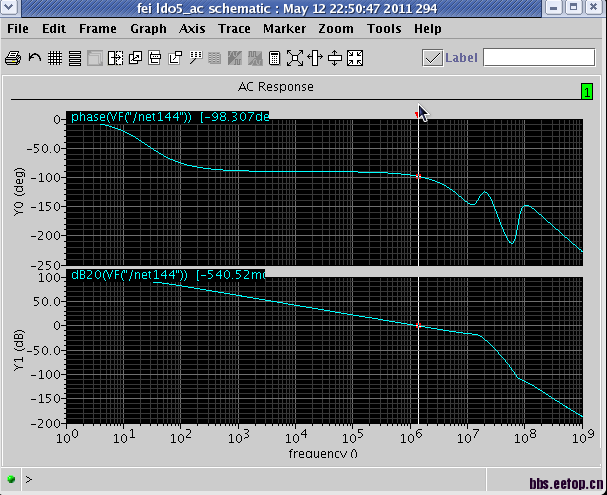

;AC 仿真的结果如下:

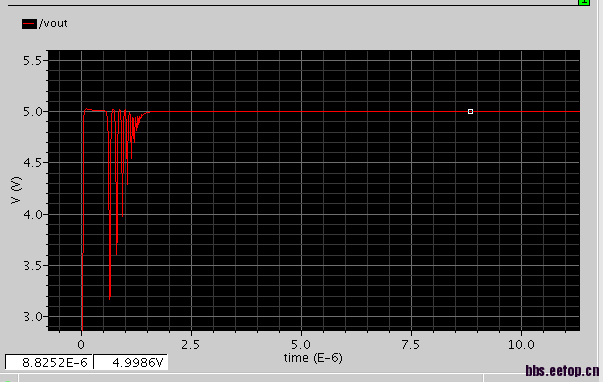

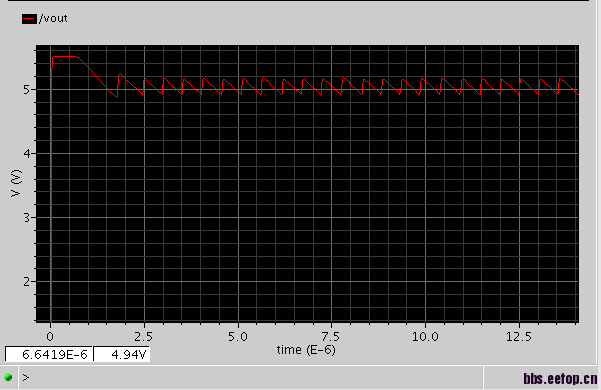

Phasemargin 和Gain margin都没有问题,应该是稳定的,但是做Transient仿真却出现了振荡:

AC 仿真是在N5点break loop的。

以上的仿真结果分别是在CL=100pf,RL=500,和CL=100pf,RL=100k的情况下的结果。

哪位大侠可以解释下不?

另外,在AC仿真时:heavy load时:Mp在linear外各管子都在saturation;

light load时各管都在saturation;

但是在transient仿真时,light load时MP ,M24,M25却在cutoff了。原因何在?

补充:heavy load:RL=500;light load =100k;regulat的范围是从5.5v输出5v。

理论上来讲CL越大时,dominant pole 会越低,PM越大,应该越稳定,在Transient仿真来看是越稳定,但是AC仿真出的PM会严重减小到30°左右,不解哦?

how do you add transient excitation, or you just do the power up. Wondering how your transient simulation is done ?

增益带宽积太高,EA的Gm太大,都要减小。ft搞到100KHz左右。

我也曾遇到过这样的问题 但是没有细细研究

电路的主极点不在输出节点上,所以CL越大,PM越小,越不稳定

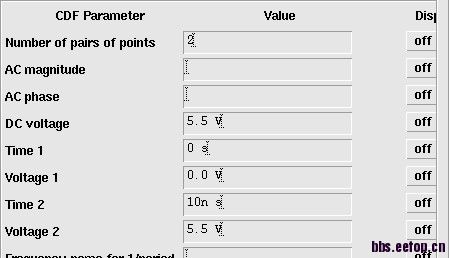

just setup VIN as follow:

other source areideal on(include bias voltage ,current source).transient simulate from 0 to 200us,step is 1ns.

由于中间那个buffer的作用,N1点电容很小,N2电阻很小,这两点的极点频率很高啊,主极点应该就在输出点处

谢谢你的建议,不过我不是很明白,能详细讲讲不,我先再看看

CL小,开关频率低,可以计算在这个周期的电压降,将RL改大试试

再补充问一下,pass transistor 应该取很大宽长比来保证大电流负载时工作在饱和区,还是应该取较小些工作在线性区就可以了?取太大的话,大电流负载时饱和但是小电流时就很难关掉,spice仿真会说它cutoff,不过个人觉得应该不是在cutoff,还是有一点电流的,至少feedback resistor会流过一点电流,应该是在亚阈值,这样对不?

理论上,LDO从上电开始直到稳态,途中会经历各种电源电压和负载的突变,只能说是一个准线性系统。这东西做稳定性分析的话光用相位裕度的方法就不够了,内奎斯特圆的办法会好一点,但是我也不会,呵呵

从咱们工程师的角度上来说,Gm小就保证线性区比较大,增益带宽积低就可以保证EA在线性区的时间,从而不会工作的像个比较器一样。(就像你的第二个图似的)。我也是个经验值,100KHz上下的Bw会合理一些。

hi

Thank you for your reply, and indeed you already provided quite a lot of information. But still without more numbers, it seems hard to detect where the problem really is. My suspects are:

1. In your circuit there are at least three loops, while you only provide bode plot for one, the outer one. There are still two more loops which can cause stability problem, the one with miller cap and the one inside super source follower. Remember there are three prerequsites that PM,GM could be used for stability judgement, and of which the first one is that loop gain itself should be stable. put stb probe inside these loops to check PM.

2. transient induced unstable. As you said Mn24 and Mn25 are off at the beginning of power up, probablydue to bootstrap, which might be worse for light load. Other transistor might also not be in proper state like cascode transistor connected to miller cap. If your LDO is used in SOC (instead of general purpose LDO), you might ask for power down and power down delay signal to control you startup sequence properly.

gm小,怎么把线性区拉大啊

电路中有复极点;米勒电容两端开环传输函数有>=2个极点,闭环传输函数计算时即可能出现复极点。具体计算很麻烦,我也没算过。你看你的增益曲线并不是-20db/dec平滑过渡到-40db/dec,而是中间有段尖锐的变化。你可以细化频率步长进行仿真,然后观察一下现象。

这篇paper你估计连标题都没看,我原来看过这篇paper,大概JSSC上的,是一个capless LDO

什么是capless LDO,就是输出那地方的负载电容很小,主极点在电路内部,那挂着一个miller补偿电容(位置不同也叫ahuja 补偿)

AC仿真多大的负载,transient就多大负载,AC没问题,那么tran也应该没什么问题。

这应该是一个正确的思路。对于一个多环系统,其稳定性的分析通常是很复杂甚至根本无解的,更不用说简单的波特图就能说明问题了。单从仿真的角度来讲,瞬态都不能保证完全没有问题的。其中常用到的一个方法就是在瞬态仿真中去strick环路中的每一个节点,如果依然稳定,那才能大致保证其稳定。

但从电路分析的角度来讲,多环系统的分析理论还很欠缺,尚无一个简单的理论可以有效地解决这个问题。

“If your LDO is used in SOC (instead of general purpose LDO), you might ask for power down and power down delay signal to control you startup sequence properly.”

可以用中文吧(先假设可以用啊)

这段话的意思是,如果LDO在混合系统中,为了稳定性,PD时需要妥善处理PD信号,这种处理的先后顺序是:先PD LDO负载,再PD LDO是吗? 为什么了?

谢谢

the title of the paper is :A transient-enhanced low-quiescent current low-dropout regulator with buffer impedance attenuation.the author:Hoi Lee,Raul Perez

同时,AC和transient的load conditions是一样的,我也非常同意你说的AC没问题,transient没问题,也非常希望是这样,但是结果并不是这样,这也是希望能得到大家帮助的原因。

把你的电路图, testbench都贴出来重新看了一下你发的图,大胆猜测是反馈极性接反了,接成了正反馈,然后输出直接串到VDD=5V。

Step up the load current from nominal to peak values according to your spec in some amount of time usually 100's of ns. Then measure the dip in the output voltage.

我也跑过LDO的电路,但是没有遇到你这样奇怪的问题。我觉得问题很可能出在buffer上,建议你首先将buffer拿掉之后跑整个电路的稳定,看看拿掉前后是否有区别?

虚线框内的小环路出现稳定性问题。

这样的结构我用过,流片也ok了

1.图2是Ti的paper,是对图1的改进,减小了buffer的输出电阻,提高该极点的频率,也改善了瞬态响应

2.这不是一个capless ldo,输出电容在uF级别

3.瞬态仿真震荡,实测震荡的可能性是99.9%.

4.把Iprobe插入PowerMOS的drain端,这样可以切断两个反馈环路,stb仿真的PM、GM结果就会和train分析结果完全一致。 但在paper中分析loop的pole & zero却是在N5处断开的,但在N5处插入Iprobe仿真结果却不能符合train的结果,这也是我至今任然未明白的。

lsh0211,非常感谢你的回复。想问一下:

1、前面的fold cascode 是不是耗电比较多啊,每个branch大概多少电流啊,我发现要比较大的电流才能减小输出电压的overshot

2、对于super buffer的设计能给点设计建议吗?

Thank you!

最近也在做一个 不过不是这种结构,是做FVF结构的caplessLDO。

仿真结果也有类似的情况,个人觉得主要考虑瞬态,不要考虑AC结果。

不稳定的原因可能在于 由于共轭极点的原因,在增益上可能会有一个小的peak。

导致增益余度有问题。

因为这个super source follower 自己也是一个 negative feedback loop, 你要看看那个loop是不是知识marginally stable。小心TI的论文,都说得不清不楚的。

呵呵,thanks!

这种嵌套类米勒补偿的LDO,主极点在N4,就算采用一般的buffer也会出现LZ这种类似的仿真结果,在N4对应节点加上CC一样大小的电容可解决问题。这主要是镜像节点不对称造成的右半平面零点。需要注意的是LZ你采用的是AC仿真,这种方式跟你打断环路的位置有很大的关系,建议采用stb做仿真,可能你就会发现其实和tran还是一致的。设计时请注意phase margin, BW, gain margin.

ps:你的增益太低,带宽太大,这个架构是可行的,多花点时间调调就好了。