请教一个自偏置差分放大器的问题

时间:10-02

整理:3721RD

点击:

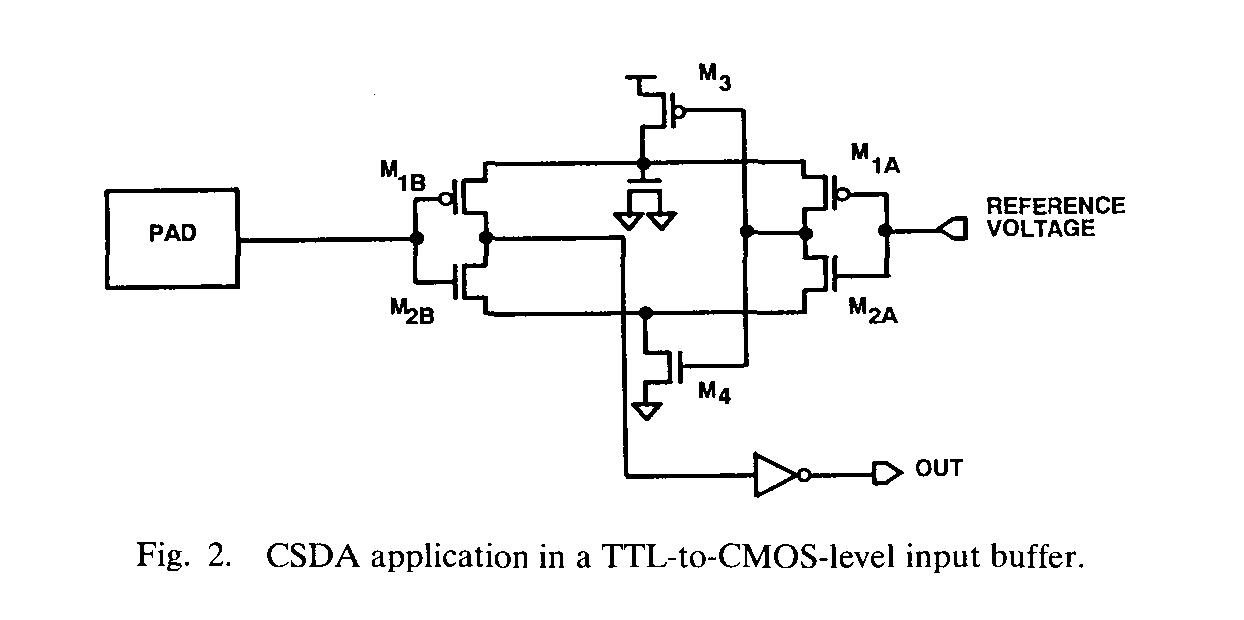

是一个经典的结构,由M.bazes提出,在allen和baker的书里都引用过,通常用作比较器的输出级(因为本身消耗的静态电流低,但能够提供大的开关电流)

在M.bazes的论文中提到在对管的共源节点加电容可以提高翻转速度(下图)

原文:"Circuit simulations showed that the addition of filter capacitors

to the sources of device pairs M1A-B, and M2A-B enhanced the switching speed of the CSDA in this particular application. This speed enhancement is the result of the additional charge supplied by the capacitors during switching transients. ."

但我现在加了大电容,不知为啥,没什么效果。

现在的电路是两级这种csda电路串联(后接两级反相器buffer),每一级csda消耗20ua静态电流,总延迟大约是20ns。如果减小尾偏置管(M3,M4)的尺寸,静态电流减小了,但翻转速度也慢了,请教大侠可不可以在这个电路上作点小改动,使静态电流减小,又不影响速度,谢谢!

在M.bazes的论文中提到在对管的共源节点加电容可以提高翻转速度(下图)

原文:"Circuit simulations showed that the addition of filter capacitors

to the sources of device pairs M1A-B, and M2A-B enhanced the switching speed of the CSDA in this particular application. This speed enhancement is the result of the additional charge supplied by the capacitors during switching transients. ."

但我现在加了大电容,不知为啥,没什么效果。

现在的电路是两级这种csda电路串联(后接两级反相器buffer),每一级csda消耗20ua静态电流,总延迟大约是20ns。如果减小尾偏置管(M3,M4)的尺寸,静态电流减小了,但翻转速度也慢了,请教大侠可不可以在这个电路上作点小改动,使静态电流减小,又不影响速度,谢谢!

qiu jiao dwffguihjkh

他上面提到特殊应用!TTL的逻辑电平与cmos的不一样!逻辑高一般比较小,逻辑低一般又比较大

你好,我看了你的这个帖子:《请教一个自偏置差分放大器的问题》我对这个结构也非常感兴趣。我想找到关于这个电路结构的论文。可是找不到。请问你能不能把这篇论文发给我sy20031983@163.com。实在不行告诉我论文的名字也行。谢谢了

TwoNovel Fully ComplementarySelf-Biased CMOSDifferential Amplifiers

我也很想知道的是初始阶段的电平是怎么样动作的,上电以后第一级反相器能够完全开启偏置MOS吗?