关于DAC SFDR的问题

时间:10-02

整理:3721RD

点击:

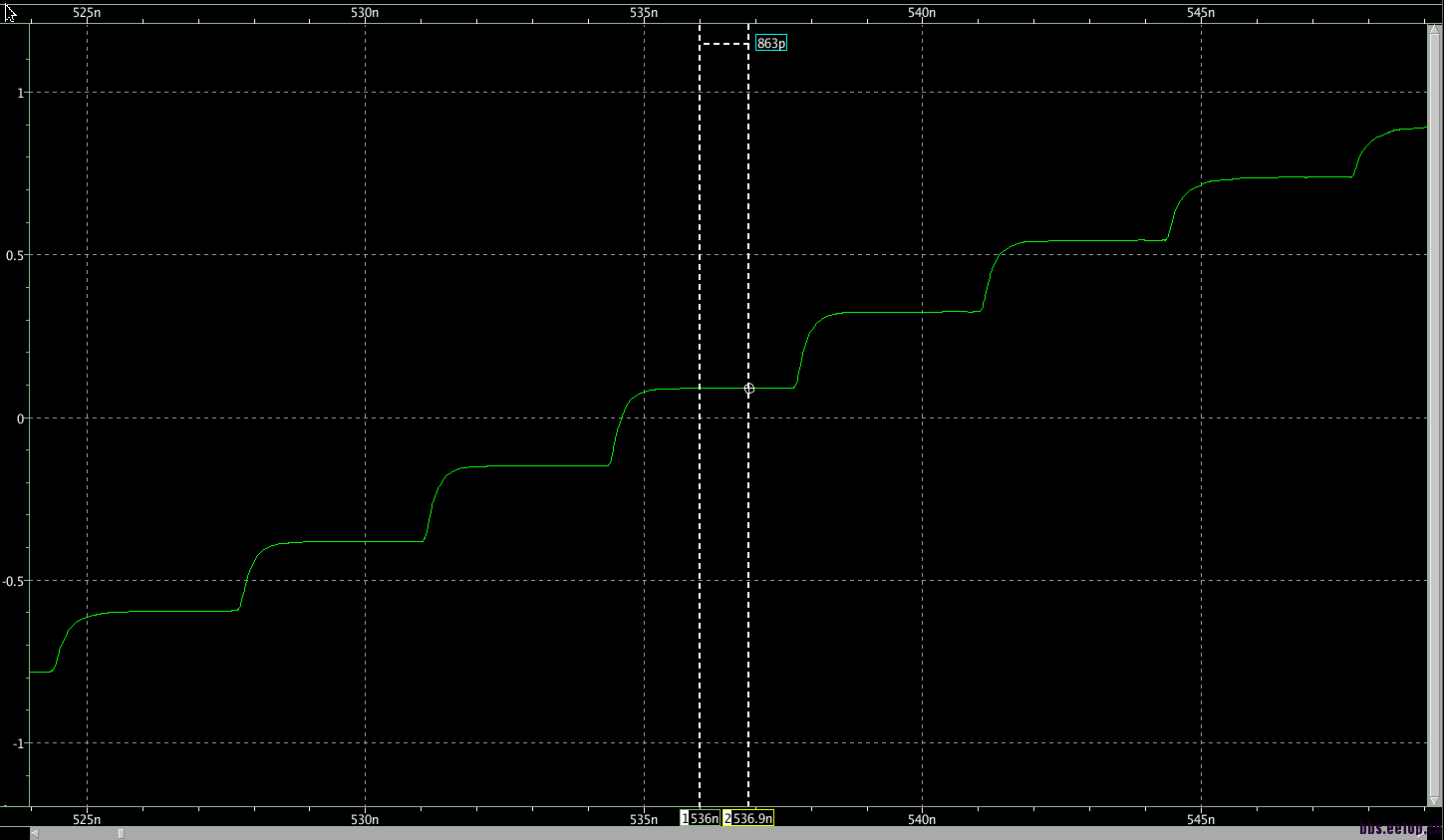

我用synopsys的看图软件看DAC的SFDR时,下图两个起始点计算出的SFDR相差11个dB, 不知道是怎么回事,有人碰到过这个问题吗?

怎么取的点?时钟频率?信号频率?

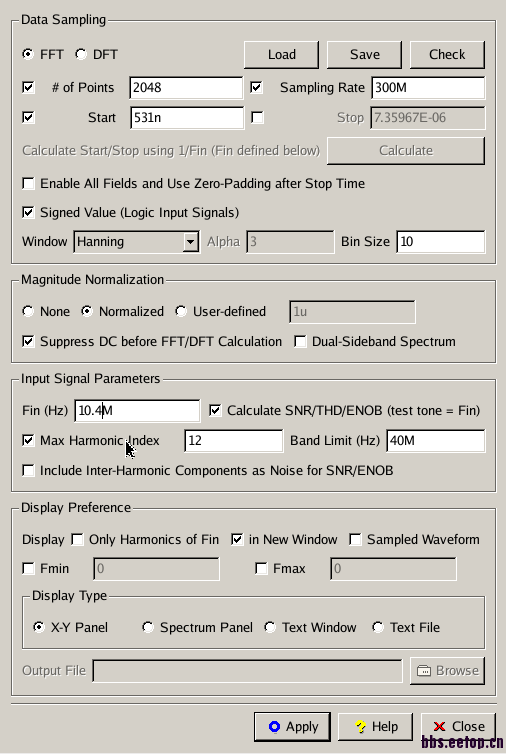

设置如下

DAC是連續信號,所以要經過filter,再取FFT

你的DAC时钟是300MHz?

那么fft采样时钟最好定得更高一点,比如300MHz×64,然后采样点数2048×14,这样FFT结果才能反应瞬态的变化,否则你都是取的每周期最后的稳定值,看上去结果当然很好了。

明白了,因为输出是连续的信号,所以一个台阶要尽量多取一些点,谢谢哈

是否考虑了频谱泄漏的问题。信号频率,采样频率,采样点数要满足一个关系式,以减小频谱泄漏。