基于TSMC 0.18um CMOS 工艺的12Bit,500M Pipeline ADC的SH电路性能分析

时间:10-02

整理:3721RD

点击:

欢迎大家指正啊,小弟最近也在下载相关论文,做对比。

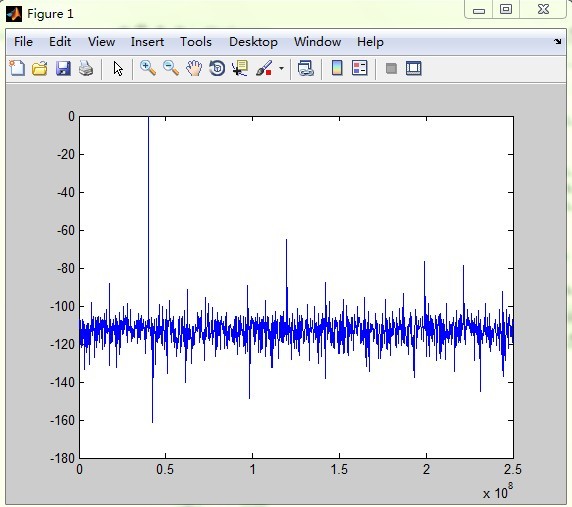

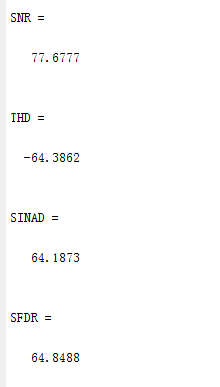

500M。谐波太高了

50M?

12bit, 500MSPS, 这是要逆天啊。

你做过12bit 500Mhz 的吗, 如有请联系我QQ 1468299862

谐波要做到多少以下,一般可以接受啊!?

fgfdgfdgdfgfddfgd

牛人就是多啊

赶快来学习。

谐波太高了

这个。S/H的SFDR就这么差了,后面都不用做了...

500k吧,500M的话,你是要逆天啊

小编没用什么特殊技能吗,只是常规电路的话挑战太大了,感觉你的谐波成分过大应该就是由于建立时间不够引起的

明明是50M啊

这个目标的确极具野心

which paper?!

卧槽,由小富人 变成蓝领工人!

dfdfddfdsfdsfsdfsdfd

我倒是做过12bit 200M的Pipelined项目,这差不多已经到极限了。你这500M是要逆天吗?