LDO相位裕度和负载瞬态

时间:10-02

整理:3721RD

点击:

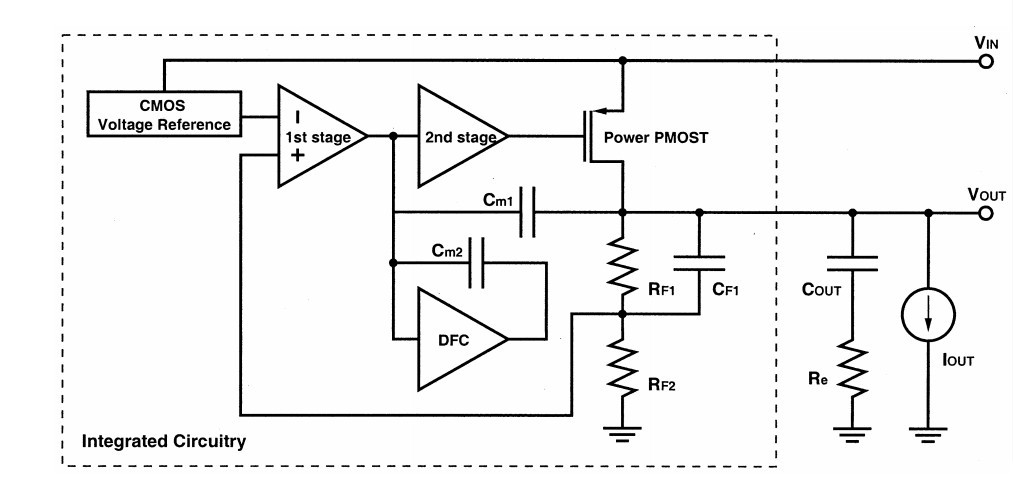

最近在做一个无片外电容的LDO,用的是2003JSSC的一个DFC的频率补偿结构。

现在在负载0-100mA的范围内相位裕度都有60°-90°

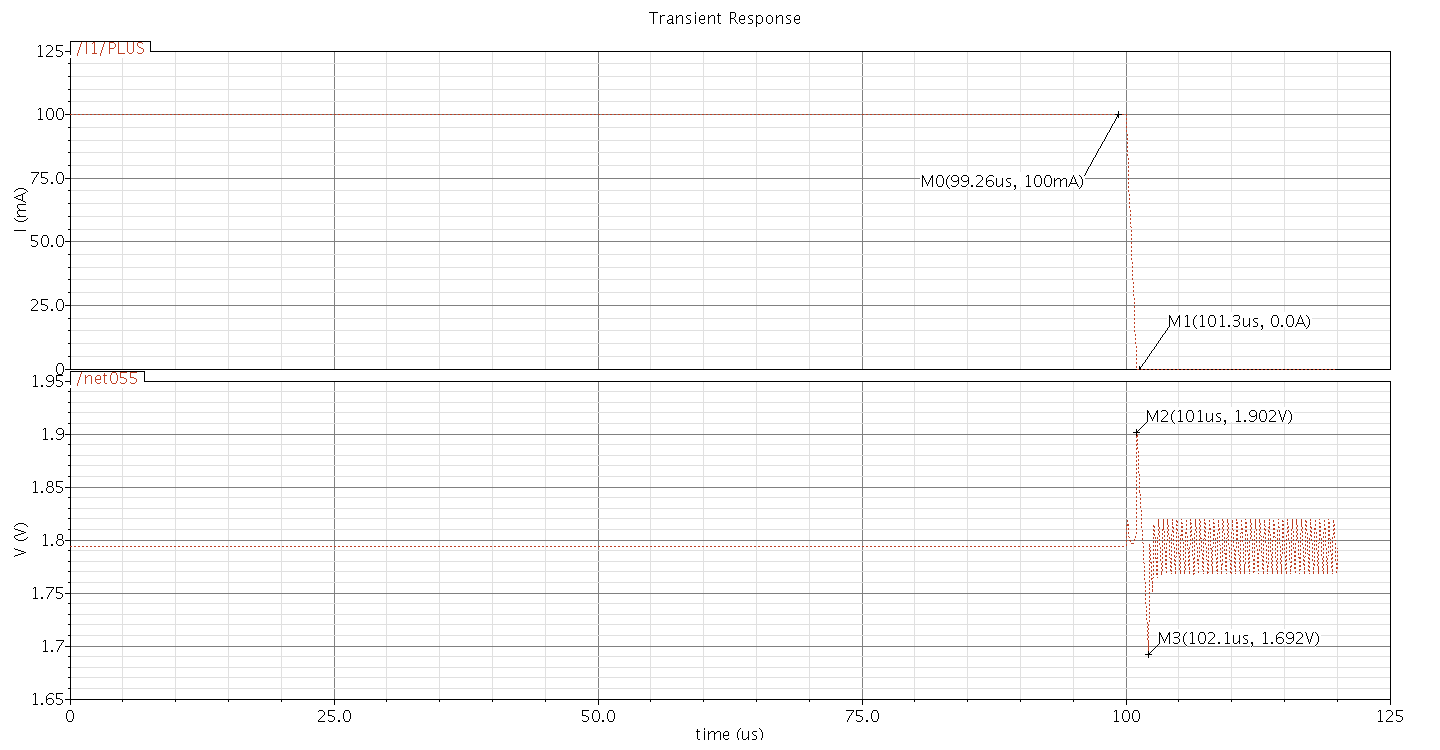

但是在跑负载瞬态响应的时候还是会振荡,这是什么原因?

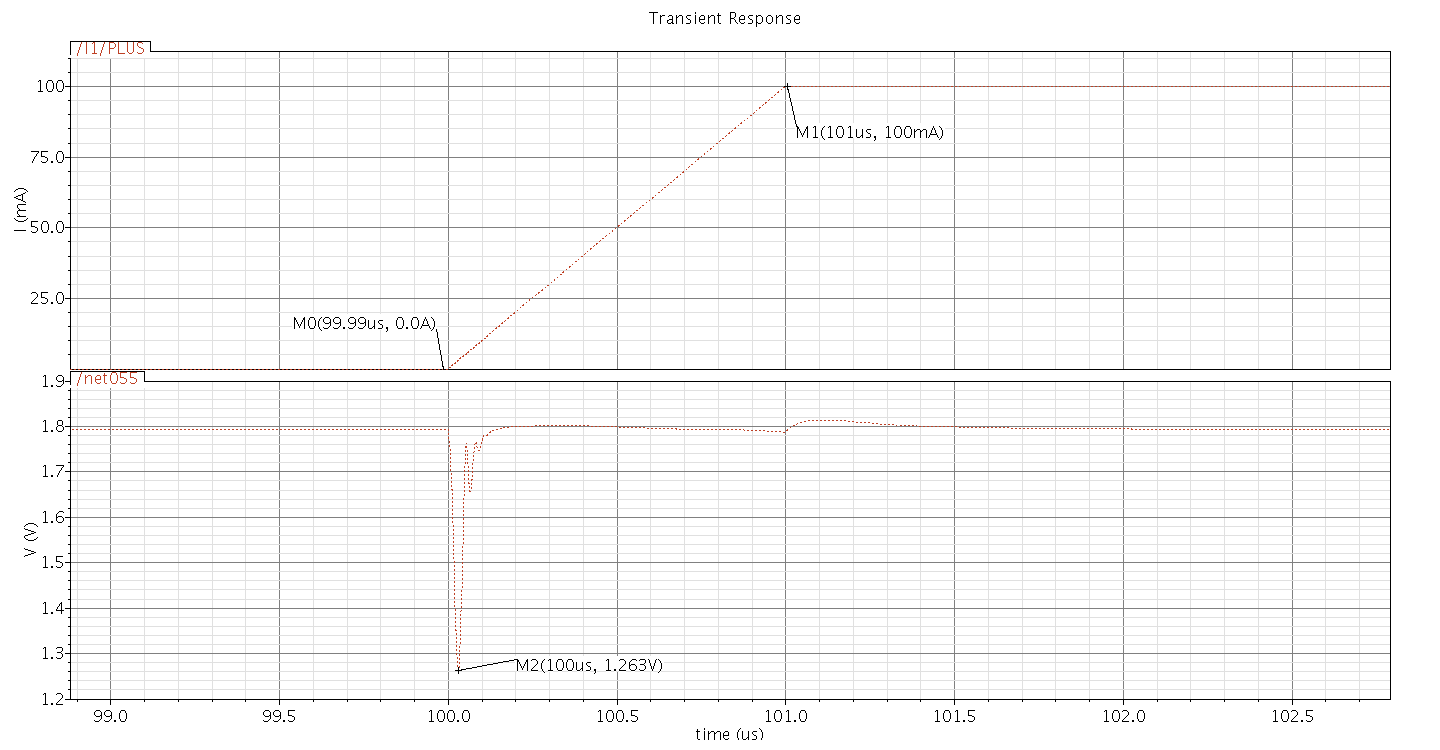

负载在1us内从0突变到100mA的时候还好,但是100mA突变到0的时候就水了。

现在在负载0-100mA的范围内相位裕度都有60°-90°

但是在跑负载瞬态响应的时候还是会振荡,这是什么原因?

负载在1us内从0突变到100mA的时候还好,但是100mA突变到0的时候就水了。

DFC

负载瞬态0-100mA

负载瞬态100-0mA

LDO小电流时相位裕度最差。这说明你的电流输出电流小时相位裕度不行。可以在输出节点旁路个NMOS diod,这样浪费点功耗,但不会使Power PMOS 的gm太小。

但是用stb仿真的时候,空载时的相位裕度也有60度喔...

相位裕度大于60度也不能说明环路就稳定,有的环路相位裕度大于30度就很稳定,有的环路相位裕度大于70度,输出还会震,stb是静态的,小信号的,并不能完全反应大信号的转换过程,tran最可靠

楼上说的好!最好也要看下增益裕度,看下trans的各种建立过程。

这样的话要往哪个方向调喔?刚发现空载时候的增益裕度只有6dB。

现在负载电流从100uA突变100mA,从100mA突变至100uA不会震荡,

从50uA突变的话是阻尼震荡。

而从0A突变至100mA是阻尼震荡,从100mA突变到0A就一直震荡了

请问这个问题解决了吗?刚好我也碰到了,如何解决这个增益裕度的问题?

在小电流的时候相位裕度最差,增益最高,可以将主极点降低,以避免次极点进入GBW,一家之言仅供参考。

所言甚是,小信号只能做参考。

对,小信号不能反映出完整的过程。