Vdsat太小了会怎么样?仿真没问题哦!

时间:10-02

整理:3721RD

点击:

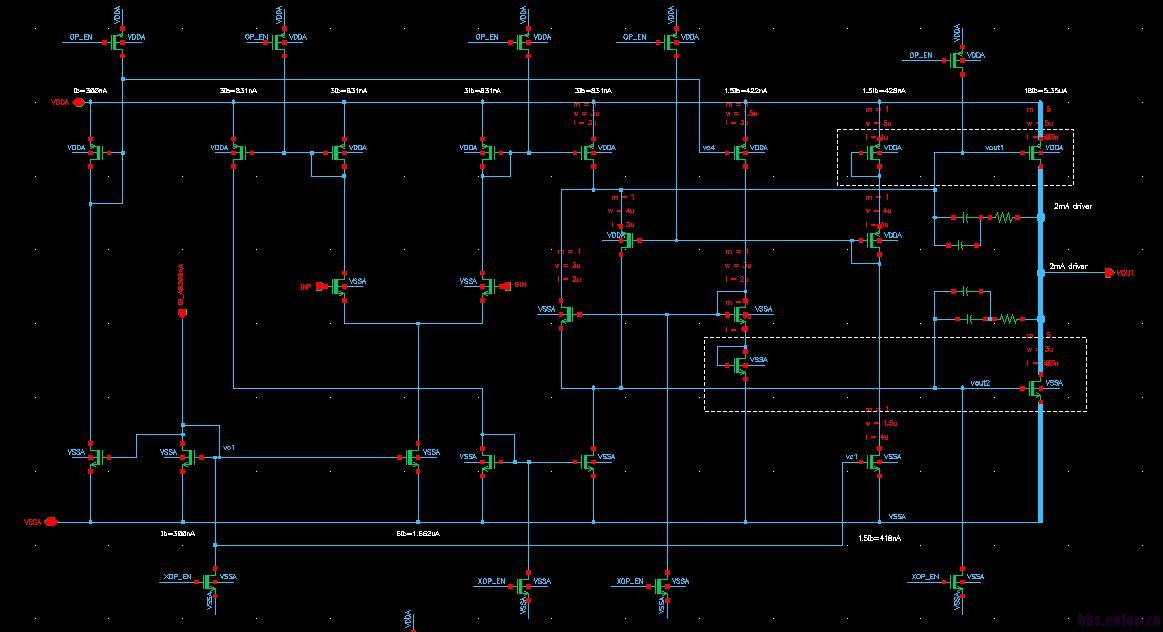

上图是一个buffer电路,为了低功耗做小电流,为了保证输出驱动电流而且节省面积没有用倒管,然后就出现了下图中M72管子的工作点:

上图是一个buffer电路,为了低功耗做小电流,为了保证输出驱动电流而且节省面积没有用倒管,然后就出现了下图中M72管子的工作点:Vgs=-610.047mV, Vth=-609.241mV, Vdsat=-66.9206mV;看着好担心,这样会出问题吗?

比如LDO的驱动管设计,为了满足RDSON的要求,输出驱动管设计的很大,但是在空载的时候,输出管子就进入截止区了,Vgs比Vth还小很多,不也是正常工作嘛。所以我觉得VDSAT很小不一定就不能用啊,对吧?

这个值不小,而且也没问题,但是我觉得你最好还是搞清楚这些管子的作用吧,看你的提问完全不对路

管子已经进入亚阈值区了,由于你的Vov很小,所以vds只需要很小就能进入到饱和区

这个输出采用较常见的跨导线性环结构,图中框出的管子,二极管连接的管子和输出管子的VGS相等,由输出驱动电流大小可以确定输出管子的宽长比,然后再设计二极管连接的管子的宽长比,来确定输出管子的静态电流;

这个classAB结构 准备用在哪儿?

为了尽可能降低输出管的静态电流,我就想尽可能增大那个二极管连接的管子宽敞比,同时又不改变那路偏置电流大小,这样宽长比越大,Vdsat就会越小,小到多少算是安全的呢?这就是我的疑问了,望高手解答

不小啦

减小静态电流,同时又要保证输出能力,在状态转换的时候,Vdsat过小是不是也会影响反应时间呢?

LCD驱动

有道理,这是一个制约条件

取决于输出支路电流的精度,输出支路静态电流基本镜像这个管子的电流

我也觉得有点像电流镜,所以担心Vdsat太小,会照成输出静态电流不准,导致整体静态功耗不准;