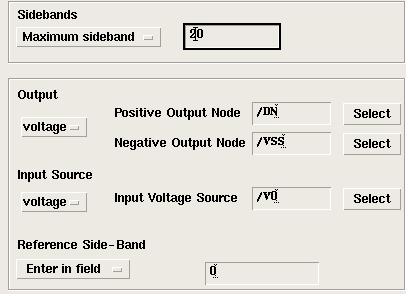

PLL中PFD的相噪仿真的问题。

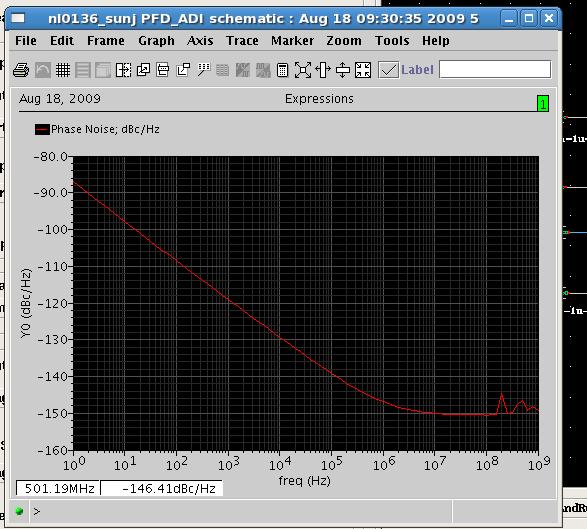

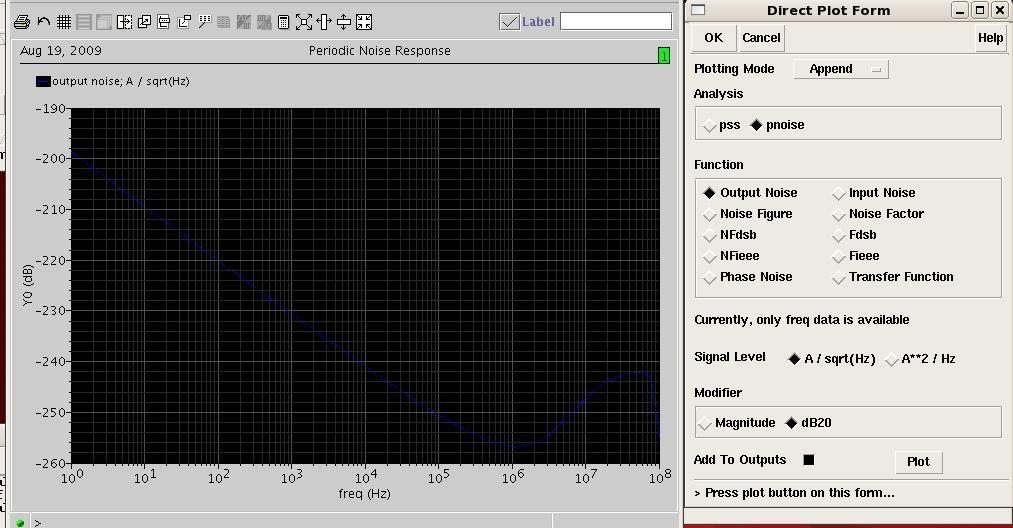

我放了0, 仿真结果如下。对吗?

是设为0,但是一般会将PFD和CP一起级联仿真噪声。

非常感谢kool!

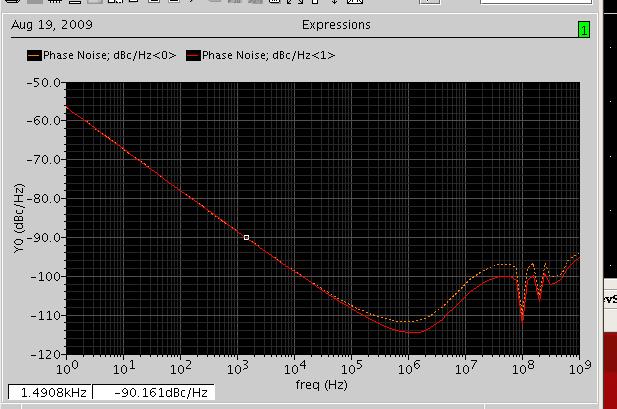

我把PFD/CP 又一起访了下,是下面的这个样子。请问:reasonable吗?

比如,我关注带内10k。 那么记下-98dbc/hz.然后,是不是把它乘上它的像噪传递函数:(N/Kpd-cp)*(Hol(s)/(1+Hol(s))), 得到PFD/CP 对整个PLL噪声的影响, 当然只是在10k这一点的大小?

其他模块也这样计算。

然后,把所有模块的噪声简单相加,是吗?

级联起来应该看CP的输出噪声电流,看相位噪声没意义。在CP的输出端接一个理想电压源来测输出噪声电流,而且在环路里面这里体现的也是电流,而不是电压。

原理基本上时正确的,但是要想清楚每个模块是电流噪声PSD还是相位噪声PSD。

你的参考频率应该是几十MHz吧,一般PFD/CP仿真到参考频率的一半就好了。

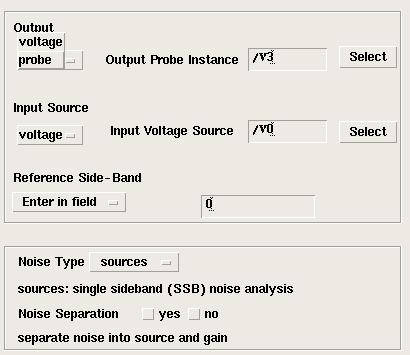

那是不是我不应该做pnoise分析? 而是应该做noise 分析? output 选 probe, 然后选中这个理想电压源?

谢谢您的指点!

谢谢提醒!

我有一个疑问:CP虽然关注的是它的电流,但是这个电流也是有相位的,随PFD而来的相位,那为什么不考虑它的电流相位噪声呢?LPF, 没有相位,所以因该仿它的噪声,对吗?

谢谢您的指点! kool is really cool!

对的,38M..是的,那我没必要仿那么高频率了。谢谢!

我现在是做得pss+ pnoise 分析。pnoise 分析的output 选了probe, 然后选中理想电压源。是这样,对吗?

还是用pss+pnosie,output选probe,仿真完成后,在pnoise的选项中选择output current noise(大概是这样,不要选phase noise就好了)。noise一般只适合线性电路分析。

电流有相位?你再仔细考虑,PFD/CP是将输入的相位差转为电流。所以CP输出这里影响PLL的是电流噪声,同样LPF输出是电压噪声。其他地方时相位噪声。

对的,Input填不填都无所谓,这个是用来算NF,等效输入噪声等等这些东西的,这里用不着。

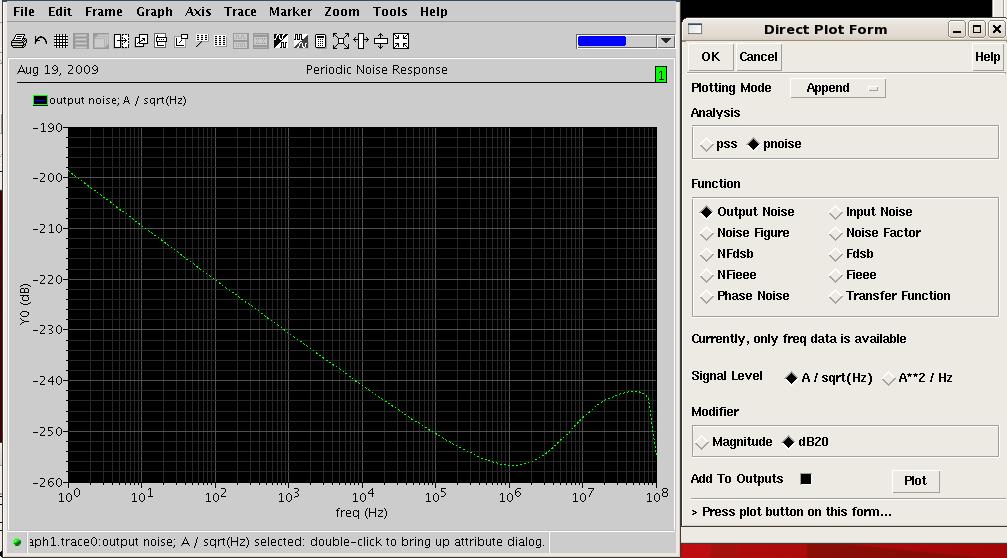

按照您说的这些设置,我又仿了一次,输出是这样子的,这样的 结果合情合理吗?还有什么不对吗?

oh my god, 怎么这么浅,看不清了,再发一遍

我想想。PFD/CP是将输入的相位差转为电流。这个我理解。可是转换成的这个电流是个脉冲电流,我的理解:它就像脉冲电压一样有相位的呀。

对了,PFD 的2个输入端我用一个脉冲源,仿真PLL锁定的情况。

仿真结果是合理的,你的理解不正确,电荷泵输出的低频电流对PLL产生影响,在PLL的系统模型中这里也是电流值,你要一个CP的相位噪声有什么用?它怎么通过环路输出到PLL的输出。你从系统模型好好理解,这是基本的概念。

从系统模型理解,我就想通啦。

非常非常感谢kool 对我的帮助! 就你一个人在这里解答我的疑惑,好感动。

不客气。呵呵。

现在开始其他模块了。也是头大呢。就我一个认做PLL,讨论的人都没有。 所以,就厚着脸皮来这里问啦,幸运的是遇见了热心的kool 还有depend... 真的好感谢。

后面还会有问题来请教啊。呵呵。

支持真实的讨论~

就是要討論阿

我也受教了

学习了,呵呵

我也正在摸索PLL的噪声仿真,受益匪浅啊。

我也正在摸索PLL的噪声仿真,受益匪浅啊。

我比较有点想不通,为什么要仿PFD的相位噪声呀?

相位噪声的定义是什么?难道不是对某个大信号振荡才有定义吗?

PFD的输出有相位噪声这一概念吗?

你看看PFD输出的频谱还差不多。

请问做仿真的时候 charg pump 输出怎么加理想电压源的?是加一个dc=0的电压源到LPF,还是加个dc=0.5AVDD的电压源到地呢?

我仿PFD/CP的带内噪声是用Spectreverlog,PFD/CP是实际电路,其它模块用Cadence系统中 ahdl库中的理想模型,组成一个宽带简单的PLL,直接看输出PNOISE,然后加上环路传递因子,20log(N/Icp), N=1