增益提升运放中辅助运放的设计

时间:10-02

整理:3721RD

点击:

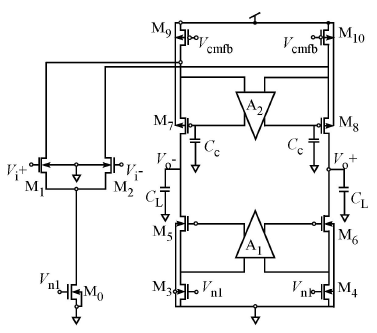

在设计这个运放时,需要考虑由辅助运放带来的极零对的影响。

有经验是:βw1<w2<w3,w1为主运放的GBW,w2为辅助运放的GBW,w3为主运放次主极点。

为了稳定,会在辅助运放输出加一个电容作补偿电容,图中的Cc。

问题是,在设计完w2(>βw1)后再另外加上Cc作为补偿电容,Cc可看做是辅助运放的负载电容吧,那岂不是使得w2变小了,甚至可能可能小于 βw1 ?

怎样确定Cc的值呢?

A1 A2增加的是它低频输出阻抗,所以按照我的理解,辅助运放的GBW略微大于主运放的3DB带宽就可以了。所以辅助运放的功耗可以比主运放要小很多。

我这个运放要用到的电路中,电路的β约等于1,这就导致辅助运放的GBW最好在主运放的GBW和次主极点之间。

我还想问一点:补偿电容Cc会不会导致辅助运放的GBW下降,毕竟Cc接在辅助运放的负载上。

或者,Cc的值究竟怎么设计?