CMOS反相器仿真时,在电平转换中的过冲是怎么回事?

时间:10-02

整理:3721RD

点击:

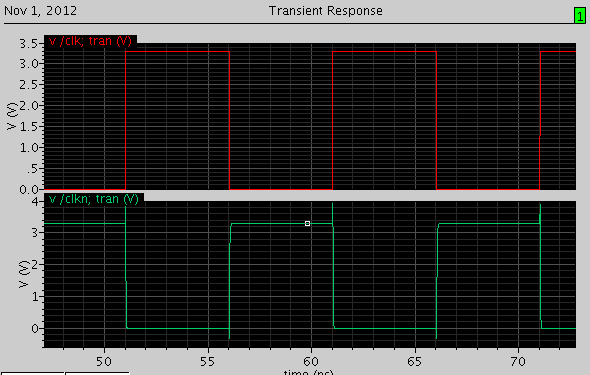

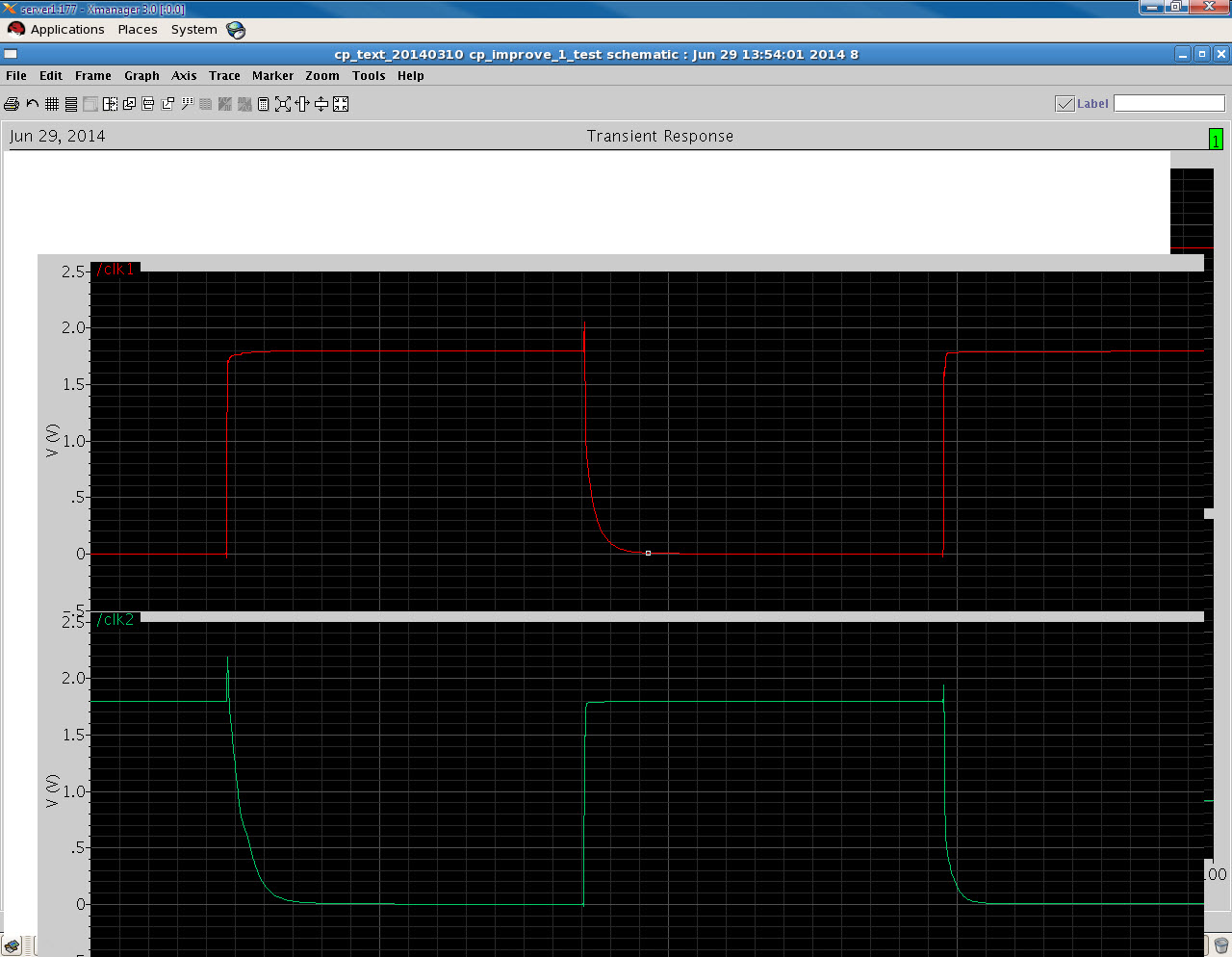

,如图,clkn的过冲是怎么回事,求教,

,如图,clkn的过冲是怎么回事,求教,谢谢

是输入耦合的吧

与Cgd有关系

高频处耦合

请问你这是用什么软件仿真的?

原来这叫过冲啊。我做DLL也碰到这问题。

Cgs Cgd引起的

对栅电容充电充过头了咯

寄生电容上的电荷下拉时放电造成的

make the inverter weak can alleviate this phenomenon

长知识了。

大侠什么意思?反相器管子尺寸要调一下?谢谢

请问大侠,反相器高电平转低电平的延时怎么尽量消除呢?

如上图所示