做过sigma delta ADC进来下!

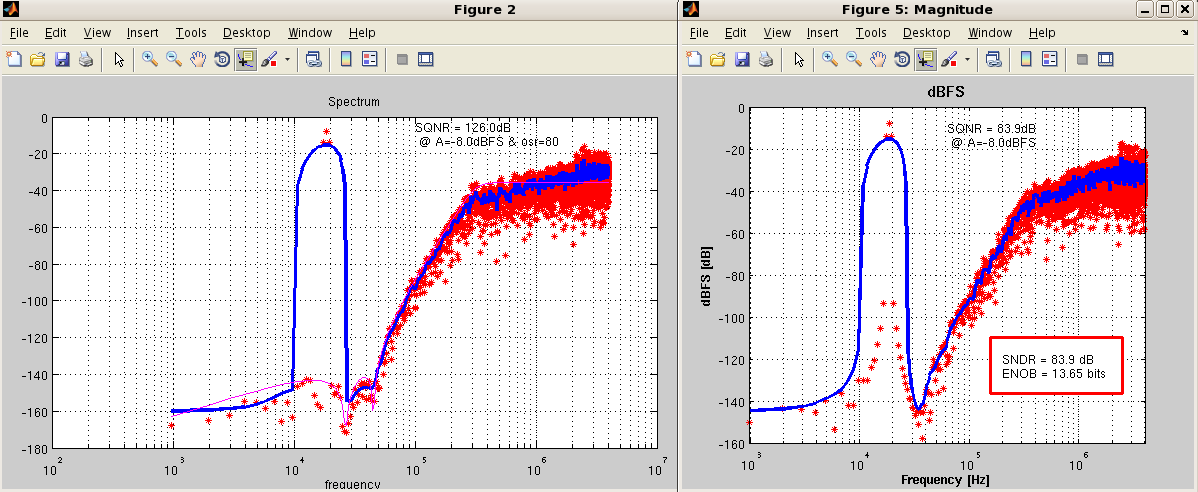

自己做实验发现,电路模拟出来的噪底不够低为什么? 从形状来开也达到了5阶整形的效果,但是电路级仿真出来做的图还是不令人满意!

Opamp gaingbw

Check your simulation accuracy, not sure what sort tool u were using.

CT or DT?

check the poles and zeros

SPECTRE

if u were using tran simulation to verify its SNR, this means no actual device noise source was introduced in the final results.

so, there was only several factors that may have influence on your simulation aside from device noise, like

quantization noise (leakage in your loop filter, intermodulation due tonon-linearity , due to modulation if any chopper exists ...)

another possible source is tran algorithm noise introduced by simulator.

I am not sure about your simulation setup or your modulator structure.

if my remember is right, i changed the tolerance setup a lit bit higher than just set the tran simulation accuracy into "conservative " and i should say this was the setup i used in a 16bit SNR SD modulator. Nevertheless, this setup is something relevant to the ckt and may not be suitable for your ckt.

my suggestion is to set the accuracy one step higher than before until the SNR reach stable. Finally, u would get the optimized simulator setup.

这仿真速度实在是要命啊

You almost have no choice. you may choose aspectre version with multi processor support and hspice may be a better alternative.

DT.it is not easy to check in circuit!

have you looked my picture carefully? you can see only three points in my first fig, but more than points in my second fig. why? BTW, i also use "conservative" in my simulator.

不好意思,之前输入法怎么也装不好。

我没有仔细看,我猜你第一个是行为级模型?第二个是CKT level?

用的是同一个窗?

我第一眼看到的是你两个DC附近噪底不一样。

我想表达的是,我印象里用Conservative是不够的,如果没有记错的话。因为后来我比较喜欢用hspice,支持多核。我的意思是你可以把tolerance之类的提高一个order再仿真一下。看看有没有变化,这可以确定你的仿真精度有没有问题。

另外的可能性是quantization noise 以各种形式的folding回来。不过这个我要看到你的具体modulator结构才能判断。

check its coefficients with the models, did you used nonoverlap clk? and pay attention to the switches' SNR

ckt调出跟行为级一致的动态特性,没那么容易的。尤其是要做高精度,很多问题都要考虑,而且要为layout留好margin

what issue?