齐纳二极管击穿电压问题

时间:10-02

整理:3721RD

点击:

大家好,有一个二极管击穿电压的问题请教一下,有经验的大侠多指点,先行谢过了!

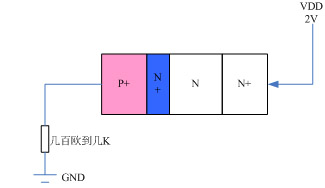

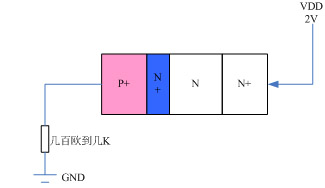

电路结构如下图,P+N+是一个非理想效应形成的二极管结构,按foundry评价,认为可能发生齐纳击穿,形成VDD到GND的漏电通路,这是不希望发生的。

查了些资料,一般认为击穿电压由P+N+的掺杂浓度决定。我的问题是:

1. 从N, P浓度如何推算击穿电压?有无经验公式?

2. 对击穿电压,设计的推算一般和实测的符合度有多高?

3. 能否有一些不同N+, P+浓度组合下的击穿电压的参考数据? 或一般工艺的齐纳管,参数是多少?

芯片目前因为该问题不能投出去,请有经验的大侠解惑,多谢了!

我对工艺了解较少,兄台是否知道一些典型zener管的物理参数,如掺杂等,和一般工艺P+N+的浓度?有什么方法判断下风险大小?

电路结构如下图,P+N+是一个非理想效应形成的二极管结构,按foundry评价,认为可能发生齐纳击穿,形成VDD到GND的漏电通路,这是不希望发生的。

查了些资料,一般认为击穿电压由P+N+的掺杂浓度决定。我的问题是:

1. 从N, P浓度如何推算击穿电压?有无经验公式?

2. 对击穿电压,设计的推算一般和实测的符合度有多高?

3. 能否有一些不同N+, P+浓度组合下的击穿电压的参考数据? 或一般工艺的齐纳管,参数是多少?

芯片目前因为该问题不能投出去,请有经验的大侠解惑,多谢了!

击穿电压6V以下是齐纳击穿,6V以上是雪崩击穿。击穿电压和二极管的掺杂,结深,曲率半径有关。是什么工艺啊,能贴下器件结构吗?

多谢指教!这是一个sram cell的局部电学等效图 , 0.13 um工艺:中间的N是Nwell, 右侧的N+是Tap;左侧的P+是一个PMOS的漏端;蓝色的N+是因为P+和tap间有poly线横跨,工艺偏差误引入的,正常不会有。我们希望寄生引入的zener diode的击穿电压高于工作电压(2V)。 物理结构示意图如下:

我对工艺了解较少,兄台是否知道一些典型zener管的物理参数,如掺杂等,和一般工艺P+N+的浓度?有什么方法判断下风险大小?