运放前模拟和后模拟的结果相差很远的原因

时间:10-02

整理:3721RD

点击:

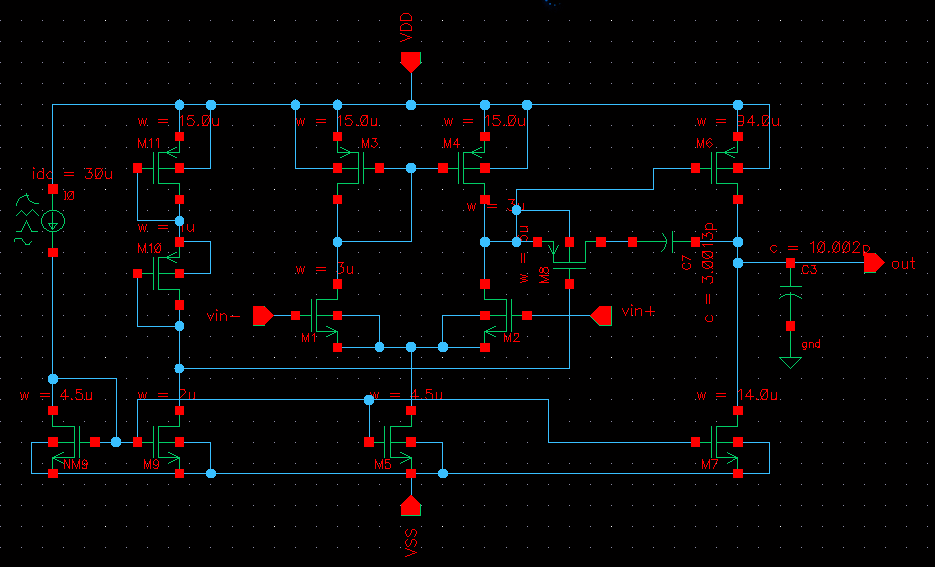

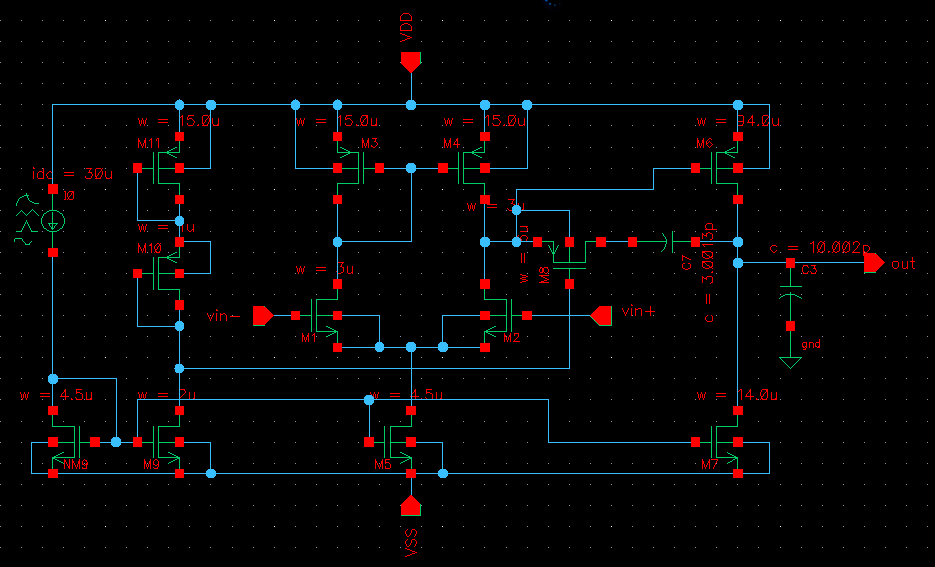

电路图如上。

前模拟的时候增益是80Db。但是版图后模拟(用的spectre)只有20dB。怎么查看是什么原因呢?

版图设计的时候,因为用对称设计,所以MoS管有些会拆成两个,和这个会有关系吗?、

后模拟求输出电压摆幅的时候,虽然设置连接都和前模拟一摸一样,但是得到的图像刚好是相反的,前模拟是先高电平,后低电平,后模拟是先低电平后高电平。刚好完全相反了。

难道有一级电路没有正常工作吗?

这是电路图

前模拟的时候增益是80Db。但是版图后模拟(用的spectre)只有20dB。怎么查看是什么原因呢?

版图设计的时候,因为用对称设计,所以MoS管有些会拆成两个,和这个会有关系吗?、

后模拟求输出电压摆幅的时候,虽然设置连接都和前模拟一摸一样,但是得到的图像刚好是相反的,前模拟是先高电平,后低电平,后模拟是先低电平后高电平。刚好完全相反了。

难道有一级电路没有正常工作吗?

这是电路图

端口对吗?后仿网表的端口有可能和前仿网表的端口顺序不一致。

看dc电流,bias电位

提取寄生参数的时候选择的是calibre view,之后是直接在生成的带寄生元器件的原理图上跑的仿真。所以端口的名字是和版图的一致的,因此也是和原来的原理图是一致的。而且都统一了大写。所以应该不存在这个问题吧?

我是直接用spectre仿真的,没有用它生成的网表。貌似用那个好麻烦,我就直接用提取出来的带寄生元件的原理图仿真。但是感觉应该不是这个的问题才对。

应该是某个管子的工作状态发生变化了,仔细检查,主要在两个输出级上,输出电阻明显变小了

看看dc工作点有没有吧

3阱工艺?

你分析.AC时,有接成负环吗?

输入NMOS M1 M2 bulk 要接地啊, 不然 M5 都被短掉了

什么工艺,输入对管的可以不接地么?

补偿的电阻干么不直接用电阻?

实在是太乱来了。

衬底都不接gnd/vdd么- -

把layout放上来看看?我怀疑是你输入管source上的电阻太大,导致尾电流源进线性区了