ADC采样、保持电路的放大器。

时间:10-02

整理:3721RD

点击:

有没有哪位高手能指导一下:

ADC采样、保持电路的放大器一般采用什么结构好?具体有什么要求?各个性能参数要设计到什么样的水平?

ADC采样、保持电路的放大器一般采用什么结构好?具体有什么要求?各个性能参数要设计到什么样的水平?

?。

先看几篇硕士论文再问不是更好么,复旦的上交的都可以先了解一下了

看看IEEE的PAPER

这问题提的。?

问具体些比较好。

关键看你的ADC,采样频率,分辨率,要求的SNR等等

同意楼上的说法,补充一下,ADC的 结构,也在考虑范围之内!

12bit,60M流水线型。

这样子,我的采样、保持电路的放大器的增益,低频带宽,压摆率。等要设计多大?

一般来说,对于ADC当中的运放,主要考虑三个因素。增益误差,带宽,噪声。

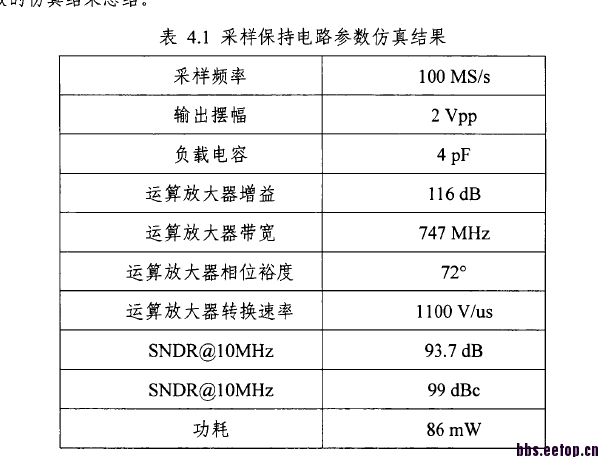

电容翻转型采样保持噪声低反馈系数大对运放要求小些,但是输入时输出共模电平要匹配,可以用折叠共源共,栅,加上增益自举。那些增益和带宽都是又ENOB,noise那些决定的,有大概的公式推导,一般硕士论文都有。IEEE的比较好的有amp-sharing和SHA-less技术,国内硕士毕设的话也不必要这么高。我看了一篇浙大2012年硕士论文,截个指标图你看看:

先学习一下哦