电压参考源——瞬态仿真分析

时间:10-02

整理:3721RD

点击:

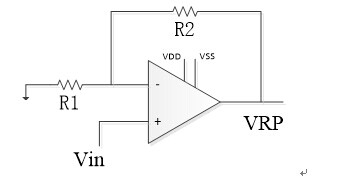

如上图所示为一个基准电压产生电路模块,电阻R1的左边连接的是共模电压0V,

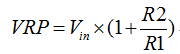

一、当给电源VDD、VSS给固定电压时,输出电压:

二、为了仿真实际电路工的工作情况,给电源电压一个上升过程,

即电源电压VDD从0V上升到5V,上升时间为10us;

电源电压VSS从0V下降到-5V,下降时间为10us;

但是这是输出电压VRP就变得不正常,

请问这是什么原因?有没有人遇到类似的问题?

在线等待你的答复,谢谢了

没图,另外,你的VSS为什么要从0下降到-5V,双电源系统?

谢谢你的回复,我已经将图片补上了,本设计中采用了双电源电压!

(实际芯片在测试时,电源电压不会一直固定,存在一个上升过程,所以想在设计时考虑)

1、输入端的参考地是什么?-5V?

2、环路稳定性分析如何?

输入端为共模电平 0V ,环路稳定,相位裕度大于70deg! 你们之前怎么考虑双电源电路的上电问题!