下图电路怎么分析透彻

时间:10-02

整理:3721RD

点击:

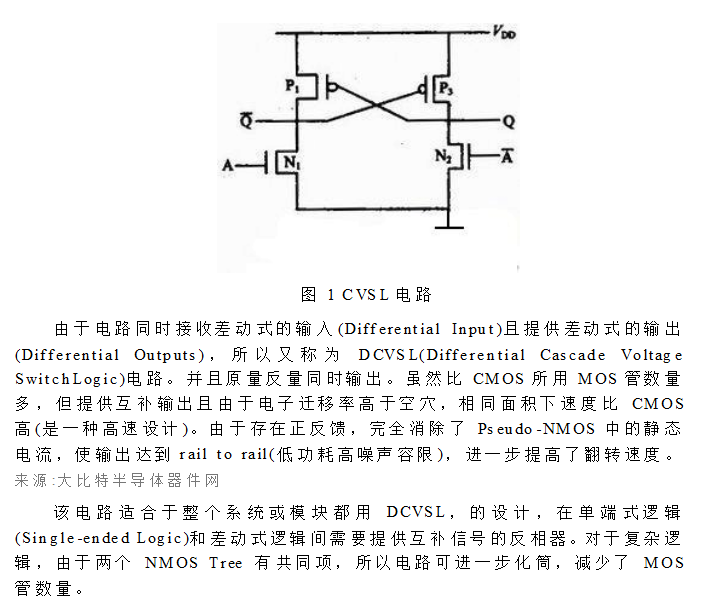

这么透彻的分析右图DCVSL电路,左边支路的PMOS接右边NMOS的漏,右边的PMOS接在左边NMOS的漏,是利用PMOS构成的正反馈提高漏的上限输出吗?正反馈不断进行,支路电流越来越大,漏最高值不断提高,当然不可能一直提升了,根据能量守恒,只能达到VDD。那么下限呢?如何实现真正的轨到轨?

解释说利用正反馈彻底消除了伪NMOS管子的静态功耗,也就是说稳定后上边的PMOS源漏电压为零,这在仿真中也得以确认(漏电压确实等于vdd,没有偏差)。压降真的可以达到零吗,岂不是PMOS源漏贯穿了?而对于NMOS而言,通过的电流只有一条通路,很大且漏极电压为VDD,全部加在NMOS上,不会源漏也贯穿了吧?如果猜测正确,那就真轨到轨了。

1、知道正反馈后,该结构中导电载流子以电子为主,迁移率大,可以缩短上升下降时间。为什么轨到轨能提高翻转速度?

2、当输入为正负1.65时,VDD和VSS绝对值很大,比如分别为+15V和-15V时,管子能正常工作吗?如果输入为正负零,会发生什么情况,能导通吗?

3、对于以上问题,应该怎么进行定量分析呀?当输入A为正时(3.3V),A非应该为负,那右边的NMOS是怎么导通的?如果轨到轨,那输出始终是VDD,增益表达式怎么定量分析呀?说着说着我就头疼了,,是不是我太笨了,想问题想偏了?求引进正道。

建议你看下:数字集成电路-电路、系统与设计、周润德译 。194页,差分串联电压开关逻辑

这不是电平转换么?

这个只有高手可以!