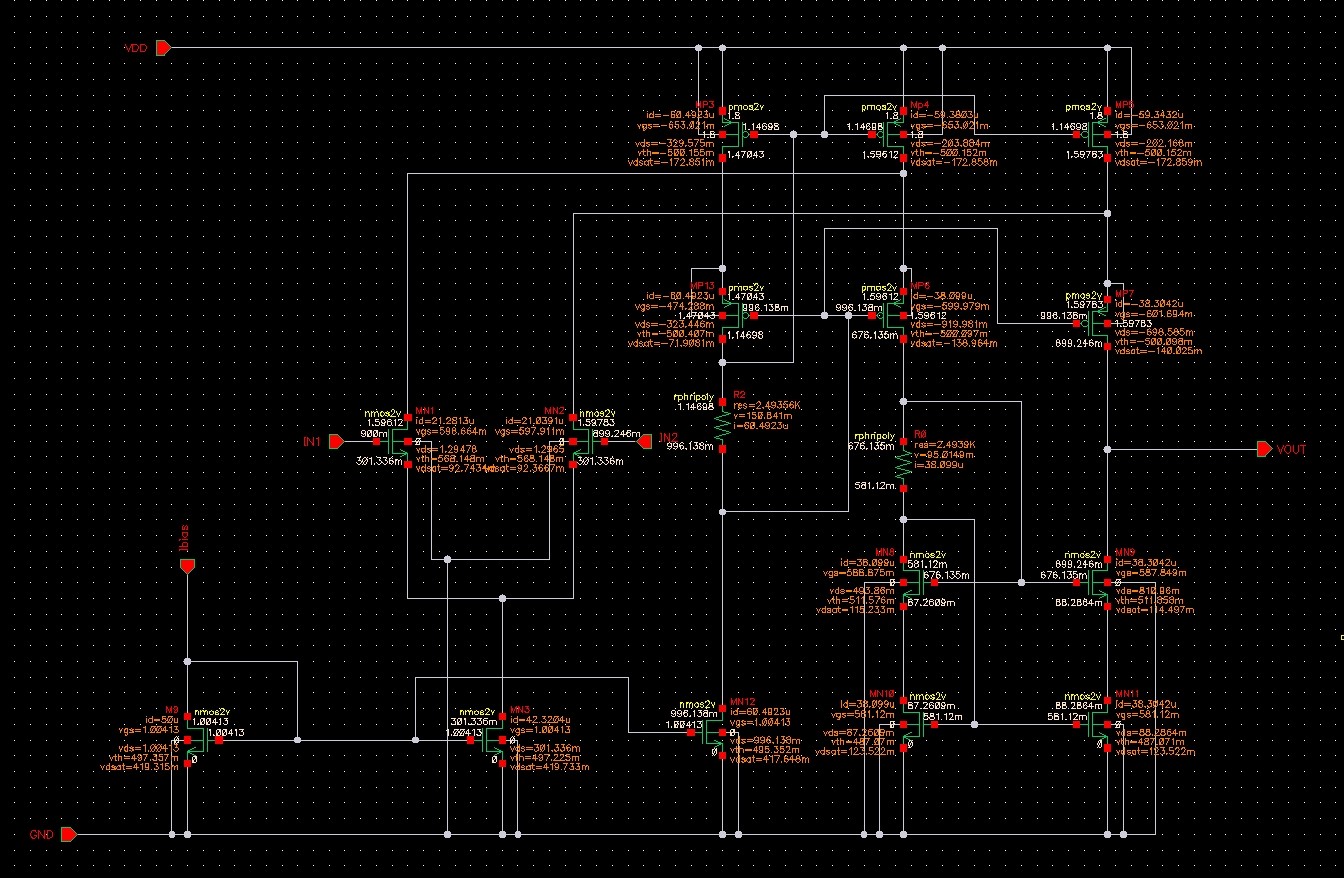

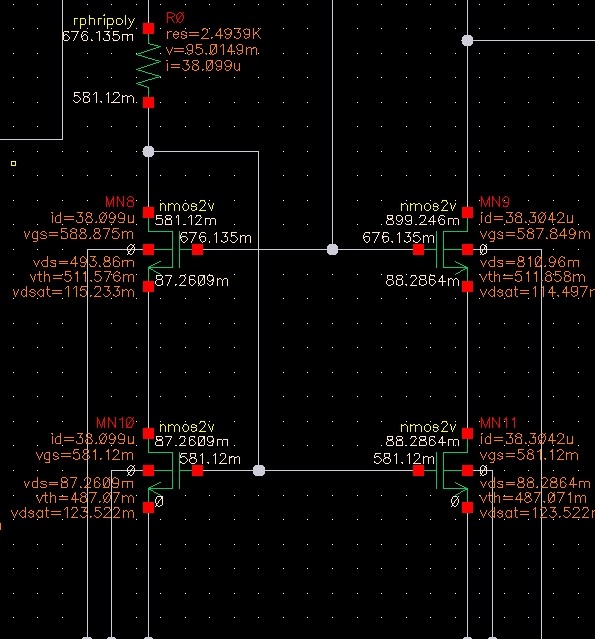

Alen书上P247设计中,MN11不管我怎么样调其Vds<vdsat.

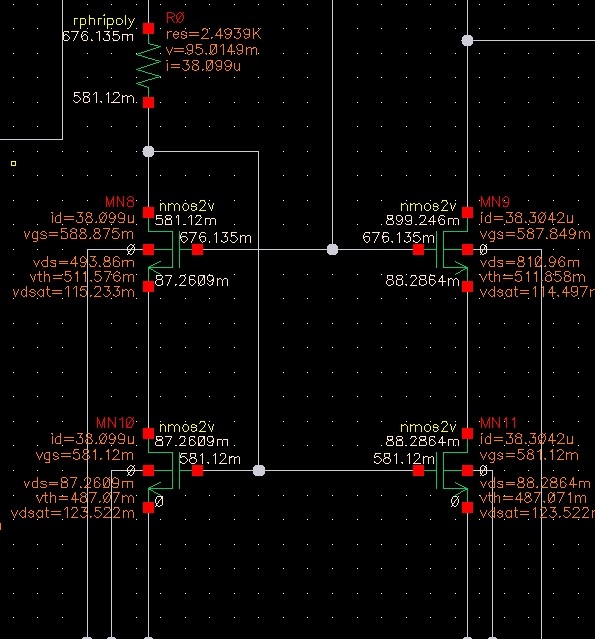

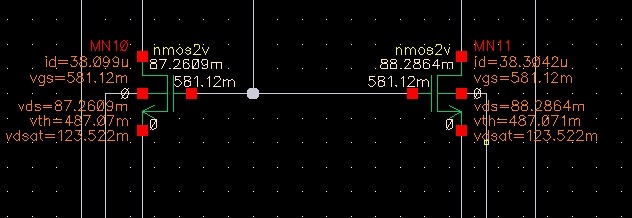

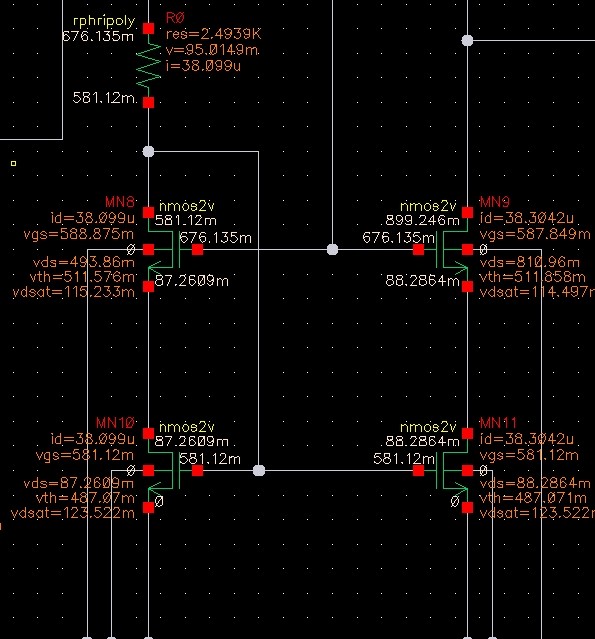

MN11的漏端电压由MN9的栅端电压控制,根据你电流,你把电阻R0增大一倍,M11的漏端电位就会上升80mV左右,Vds11就有160mV左右,Vds就大于Vdsat了

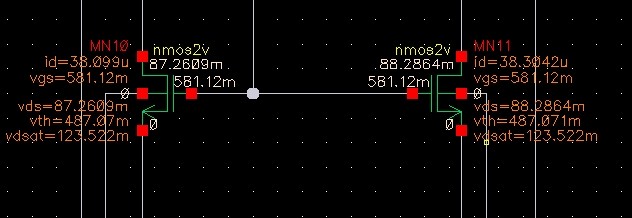

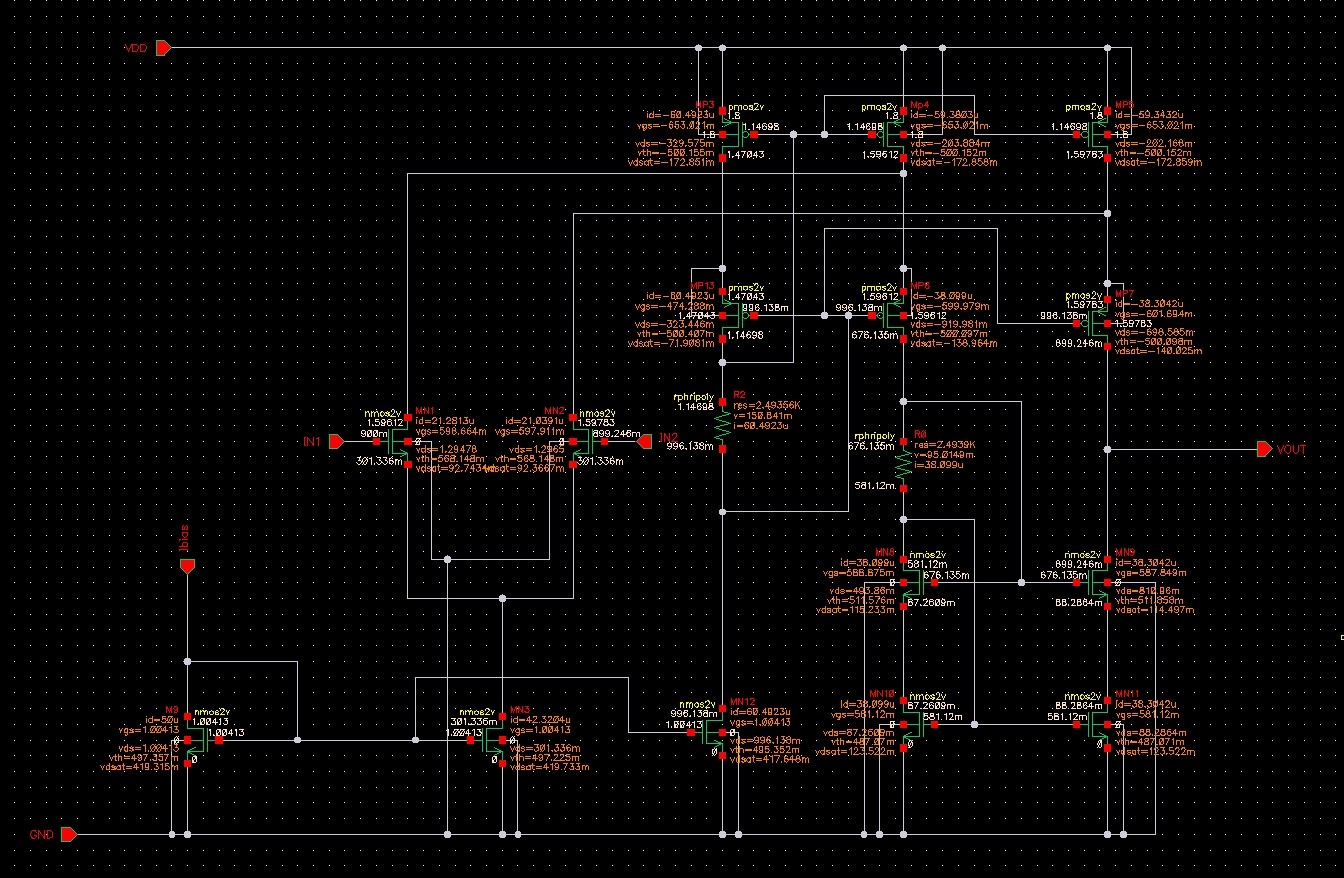

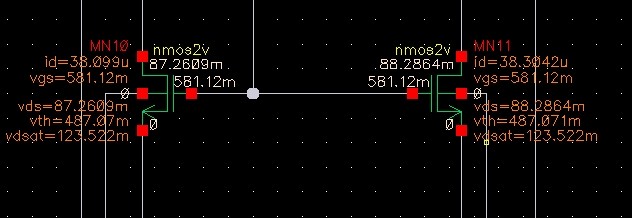

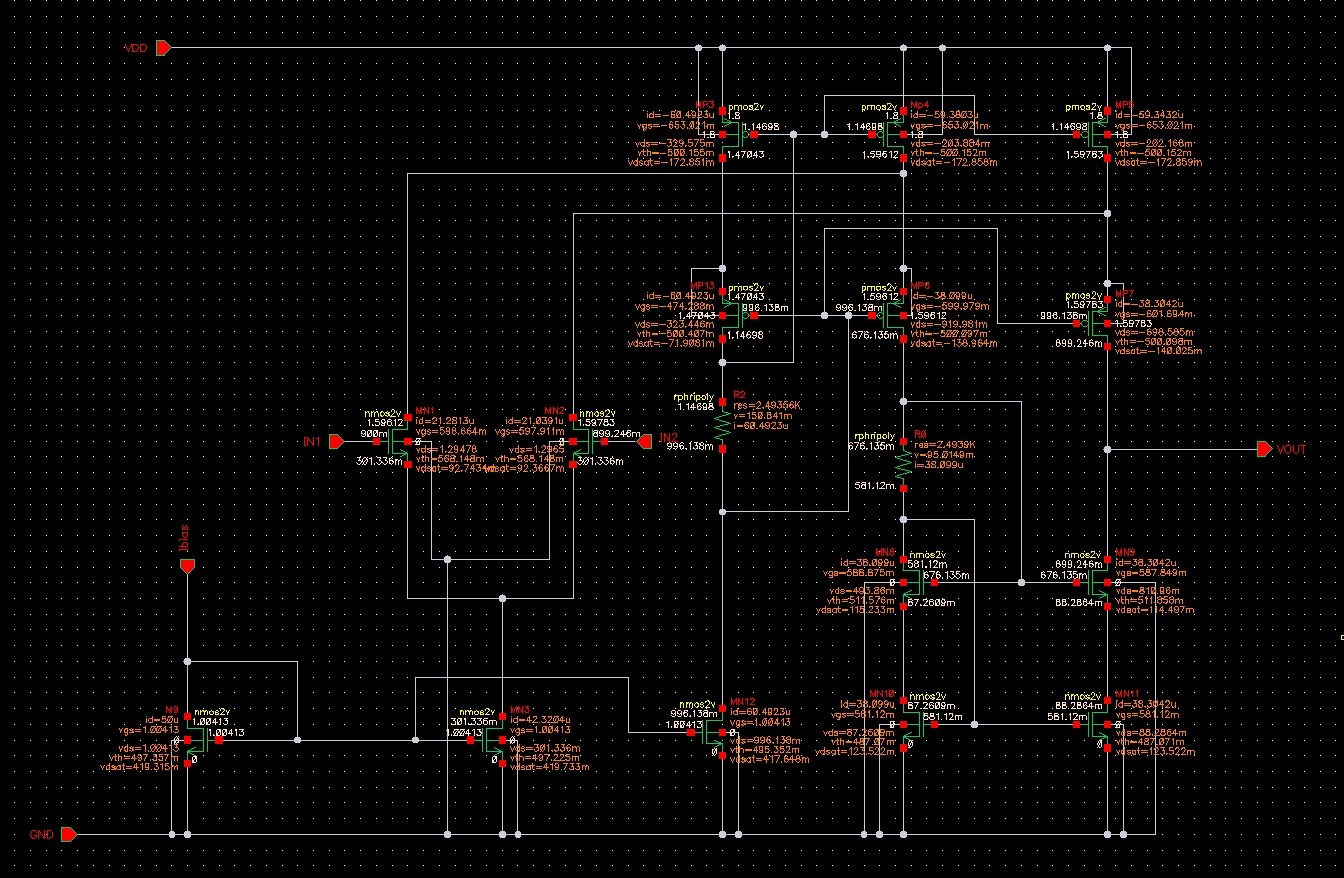

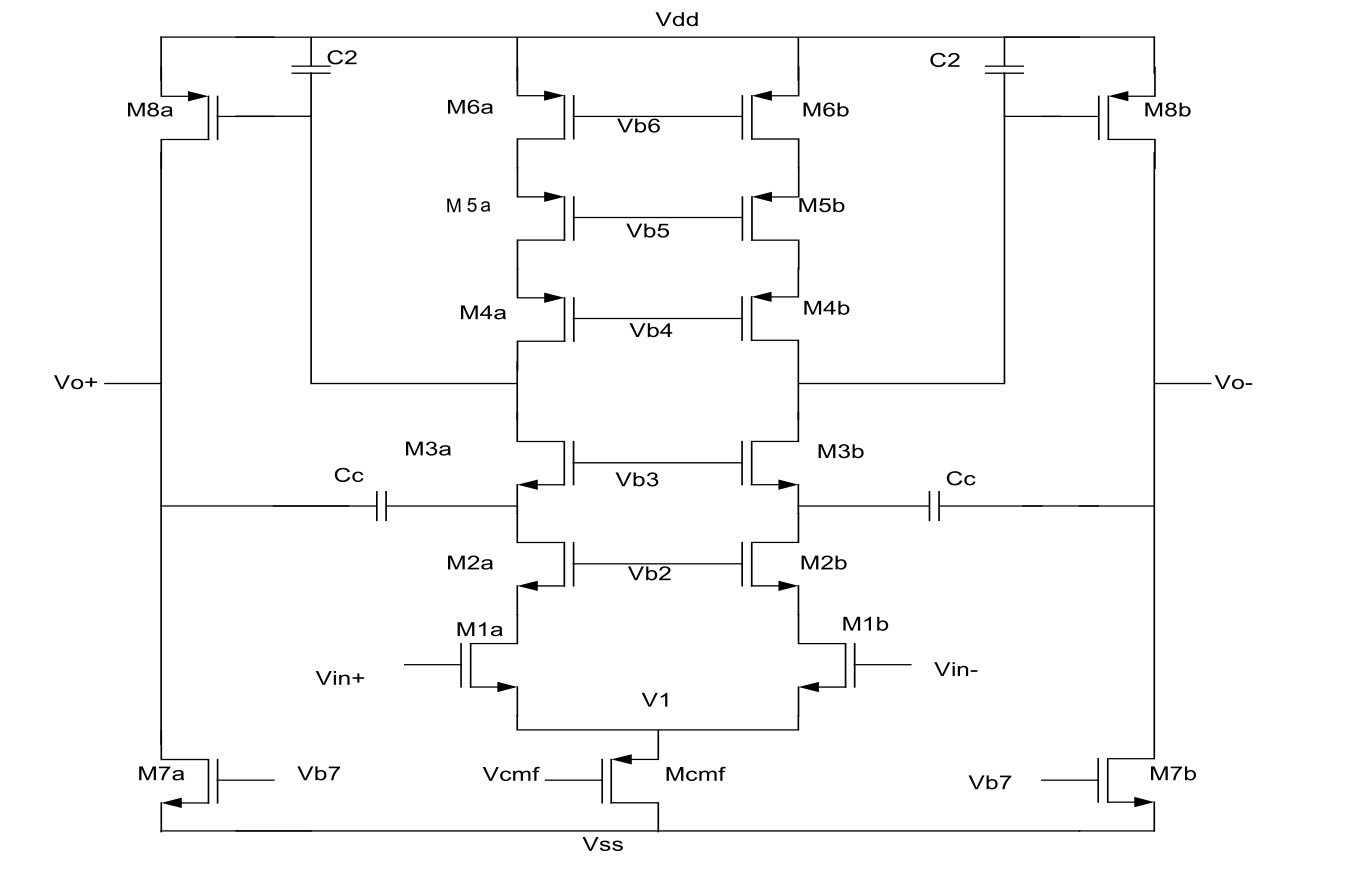

谢谢大神指点,可是我重新定的设计指标,由于功耗很小为<0.16mw,所以我选输入管下的偏置电流为30uA,其他三条支路都为15uA,可是仿真出来的其他参数都达到目标,就是MN11和MN10处于线性区,改变电阻翻倍也不行,是不是我的MP4、MP5选小了呢,如果将MP4、MP5的电流选大些(其他支路的电流就会相应减小)我的Av又上不去。求指教啊。

cascode 管子MN8消耗了差不多500mv的Vds,而MN10才100多mv,所以,你要增加MN8/MN9的W/L比例,选择小的L和大的W。

电路基础,在MP4的漏端节点有一个KCL,MP4,MP5是偏置电流源,每个管子的电流最好要大于等于输入差分对的尾电流Is因为差分对工作时最大可以使得一个管子流过电流为0(理想)另一个管子流过为尾电流。这样可以让MP4的电流为30uA,MP4漏端连着的另外两条支路分别为15uA, 15uA,你要这样设计才对

正如lishiliang所说,你要让mn10和mn11饱和,加大那个电阻就好啦,你还没牵涉电流选择的问题呢,先要学会调工作点才能优化设计。

你那个cascode看着不象用的是最小length选择小的L又会导致我的Rout减小,从而导致增益减小啊,我的增益就满足不了75db

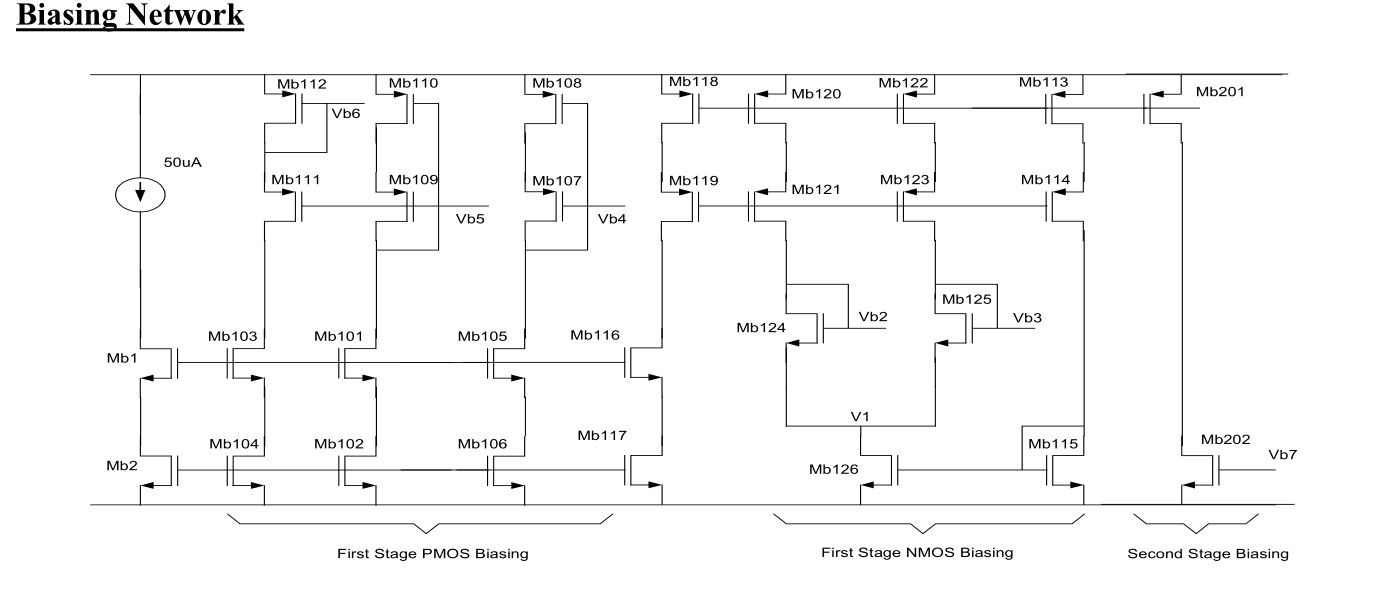

我刚刚尝试了你说的MP4=MN3=30uA,这样最下面的两个管子是可以处于饱和区,但是,MP4,MP5,MP3三条支路的电流分别是36、36、30uA,加起来超过了我的功耗,我要求的功耗P<0.16mW,还有我的增益一直都是50db附近,我增大MP4,MP5,MP3的W,以及将MP7,MP6的管子W/L增大一倍,还是没有什么效果,或者我增大MP4,MP5的L,其还是不能达到我所要的75dB,另外,很多人说我的偏置电路不好,最好不要采用这种,你能推荐一种比较好的偏置电路吗。最近在读一片论文的时候看到下图所示的偏置电路,(如上图)但是看不懂为什么。我的折叠共源共栅电路还有很多问题啊,都不知道怎么改进了。为什么要用这种自偏置?在运放实际工作会进入线性区,你仿个瞬态就知道

说实话,你这个太简单了,所以没人回复,Jocob的《CMOS电路设计仿真和布局》好好看看,这个有偏置电路,很实用

学习中!