charge scaling dac设计中遇到的问题

时间:10-02

整理:3721RD

点击:

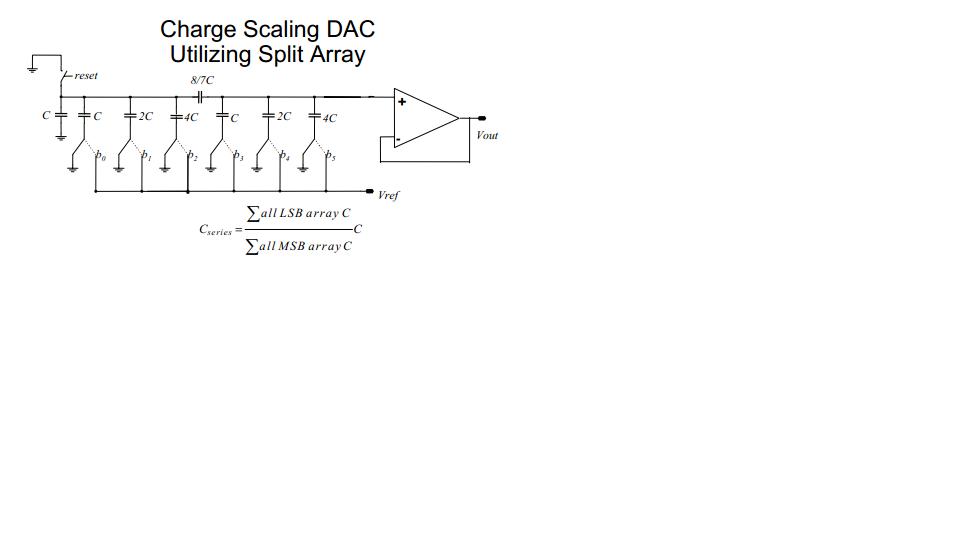

本人刚开始设计电容式DAC,书本也看了几遍,发现有些问题还是不太明白:

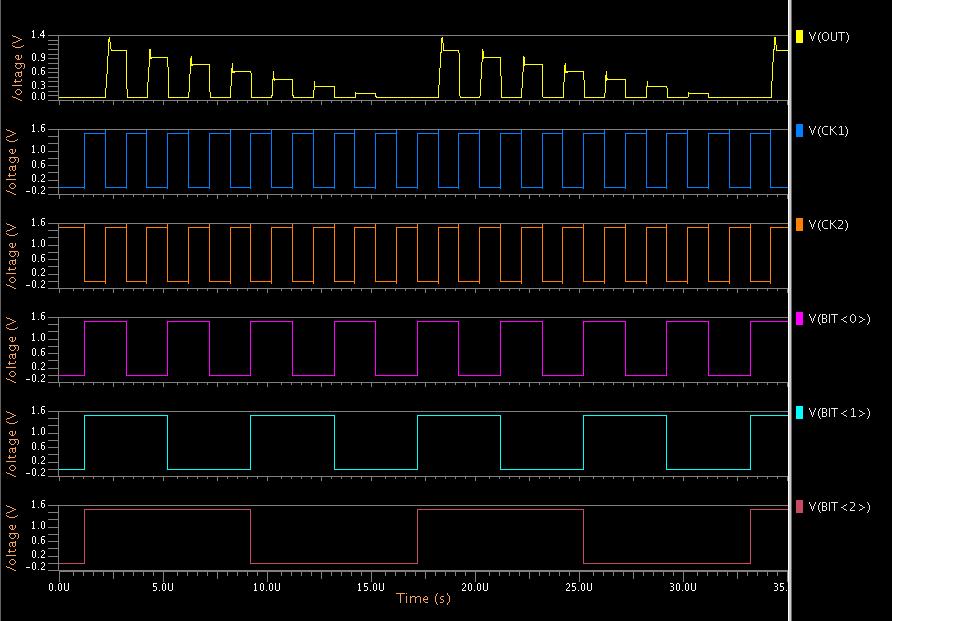

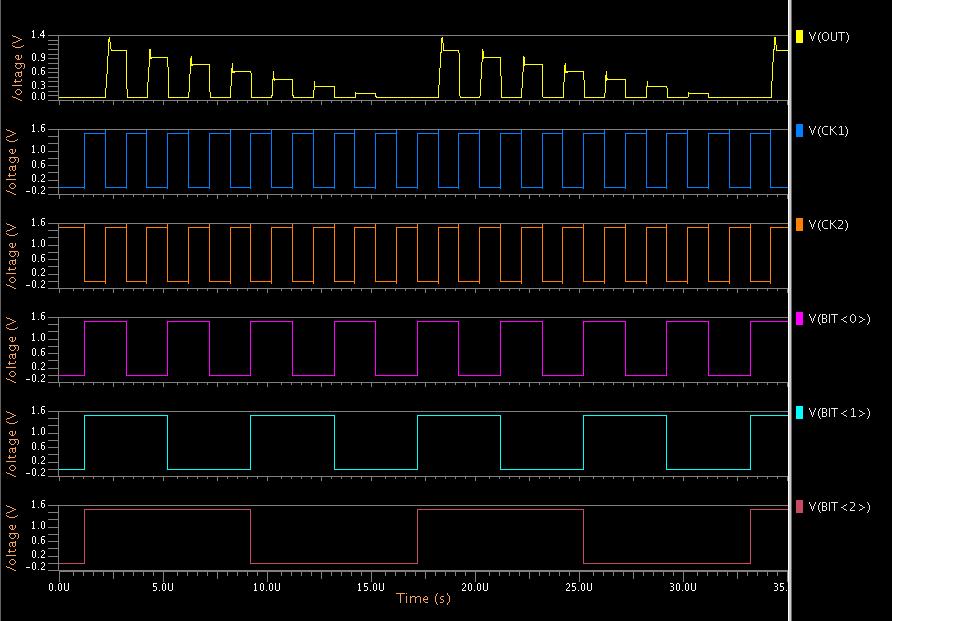

1. 这种电容式DAC, 都要采用非交叠时钟,当CK1为高时,电容两端放电;当CK2为高时,进行转换。时钟应该是DATA速率的2倍,那意味着输出波形是不连续的,这种理解对吗?还是我需要后面再加电路让输出变连续?

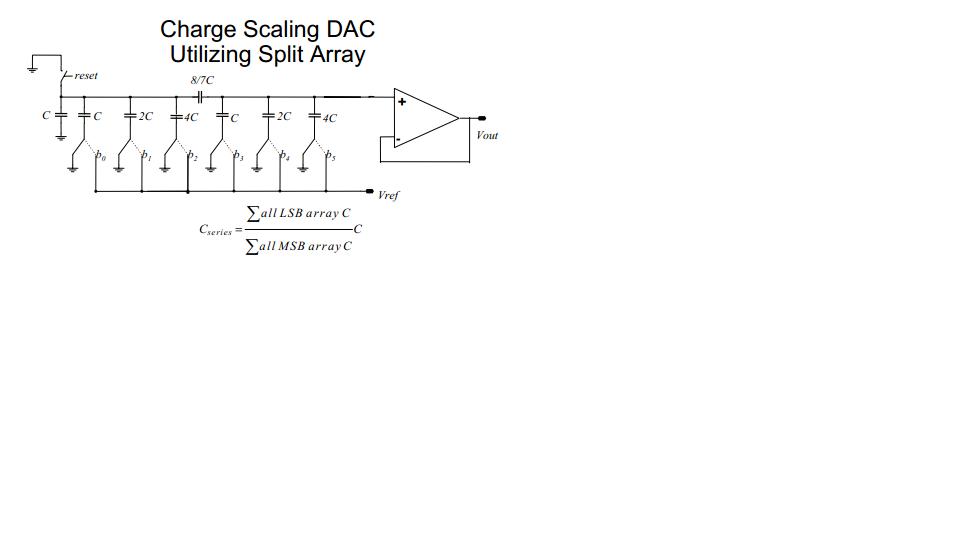

2. 书中有写delta c/ c的比率确定了这种DAC能够达到的位数,那么如何计算一个单位电容的大小?

3. 学习DAC设计,有没有什么好的资料和论文,请推荐一下,谢谢。

1. 这种电容式DAC, 都要采用非交叠时钟,当CK1为高时,电容两端放电;当CK2为高时,进行转换。时钟应该是DATA速率的2倍,那意味着输出波形是不连续的,这种理解对吗?还是我需要后面再加电路让输出变连续?

2. 书中有写delta c/ c的比率确定了这种DAC能够达到的位数,那么如何计算一个单位电容的大小?

3. 学习DAC设计,有没有什么好的资料和论文,请推荐一下,谢谢。