流水线ADC设计失败,请教!

1. 输入正弦信号,时钟超过10MHz后,负半轴输出开始出错,随着时钟频率进一步提高,出错的位置逐渐向正半轴方向蔓延,直至整个正弦波形都出错,但当输入位于0附近,也就是正弦的中间位置时,几乎不会出现转换错误。

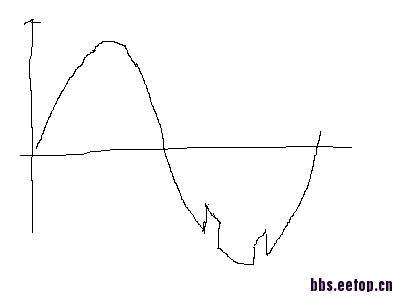

2. 测试波形实在很乱,但简单抽象后,极致的情况就是下图这样,这里画的是一个小的错误,误差大时上半轴的输入,输出都会跳到下半轴去。

3.输入直流测试,发现当时钟频率提高到10M以上时,第一级流水级的某一位数字输出会发生跳变,导致转换错误。这个跳变的位可能的第一级的任何一位,或者是某两位一起跳变,且除去跳变的一位其余ADC数字输出位都不动。

另外,测试时发现,虽然输出错误,但并没有lost level的情况发生,也就是流水级的残差输出并没有溢出。

4. 根据这些测试现象,我只能猜测比较器输出到MDAC的温度计码还是对的,但是到编码电路后就出了问题,但电路上的分析找不到头绪。希望各位牛人给看看,多推荐点可供排查的可疑点,请多指教哈。

图没粘上,再发一遍

timing 查过没有,clock 小于10MHz 没有问题么?

input fully differential ?只出现在负半段?

这个要用各种方法排除,慢慢缩小范围

以前我最喜欢debug了,呵呵

感觉是比较器问题,然后MDAC传输曲线进入了错误的区间

做后仿真的时候没有仿出来问题吗?

这个有点难猜测,因为不知道你的设计。

没有只出现在负半段,是时钟频率升高时负半段最先出问题,但随着频率继续提高,错误会蔓延到正半段。10M以下没问题,动态性能都很稳定。我也喜欢debug,可惜木有思路了。

我开始也感觉很像,但如果MDAC到了错误区间,应该会造成流水级输出超出下一级的输入范围,表现在ADC输出上会有一段模拟输入信号区间都转换到一个数字输出上,但这个芯片没有这个现象,虽然分辨错误,但可以看到错误的那一段区间内还是有它的线性度在的。您再给出出主意,看看我还漏掉了哪些点,谢谢啦~

各个模块的后仿都做过了,比较器、MDAC、采保、输出校准,是把模块版图提出的网表放在整体电路中做得后仿,性能都可以。不过确实没有把它们连在一起做,时间太长了,您看在后仿这还有哪些能做的排除下问题不?谢谢啦~

前辈如果给提供些芯片出问题后debug的思路和方法,分享下自己debug的经验,我也不胜感激呀:)

怀疑是比较器输出给数字校准电路时timing太紧

看来MDAC没错,但是比较器出的数字码(真实结果)没跟当级的MDAC传输曲线(正确结果)匹配上,所以输出看上去就是一部分码的权重出了问题,我猜是bubble killer或者是digital correction有错

你现在是clock频率快了才出现fail,那跟输入频率有没有关系?

由于clk频率低时,function正确,所以hold time应该没问题,看上去像setup time问题,但20M对数字电路应该不是问题,但还是需要check。还有一点就是MDAC里的comparator有没有reset,没有reset就也许要较长时间才能recover,就相当于有个迟滞,当大到超过0.5bit margin,事情就大条了

这个问题有解决吗?同病相怜啊,我也遇到了这个问题,一个芯片内部Iq两路这样子的ADC,一个出现这样子的情况,另一个没有。真是头大了。

我发现在我不接输入时,没有问题的ADC输出的code刚好是中间值32;但有问题的这个输出时44.才6bit。

灌入正弦波, 也是在中间某个区间,突然整体值变大了一些。如果没有这个shift,就是一个很好的正弦波结果。

回去查了一下给数字校准的timing,都是电平采样,没有沿采样的触发器,timing是不是要求就不是很高了呢?

嗯,能给细说说bubble killer是什么吗?不太了解呀,谢谢啦

fail和输入频率没有关系。

比较器有reset,回去再好好看看timing,现在小抓狂,还好有大家帮忙:)

您那debug有进展一定分享呀

单说bubble killer,主要是应对于高分辨率单级电路的比较器温度计码输出给出亚稳态的情况,你可以搜索‘火花码’,俗称气泡;级电路比较器用的越多,越容易产生气泡,bubble killer是一个简单的数字逻辑电路可以恢复出正确编码。

但看你的数字码加权给出的波形,就是在一部分位置上出现了权重的缺失,就仿佛,比较器给mdac的结果是正确的,mdac也给出了对的余差和传输曲线,但是比较器送给输出的某一位(或几位)数字码却是错的,让那一位的权重没有体现出来。所以猜测是一些数字辅助电路出了问题。同时又和采样频率相关,可能是数字逻辑的dff出了问题。还是得仿真才知道。理论上是应该可以重现这个结果的。

哦对了,你最后数字码总要通过dff同步吧,这里也有可能有问题

就仿佛,比较器给mdac的结果是正确的,mdac也给出了对的余差和传输曲线,但是比较器送给输出的某一位(或几位)数字码却是错的,让那一位的权重没有体现出来。

应该比较接近真相了,一般仿真不会发现,但是后仿真以及极限corner会出现。

肯定要后仿,r+c+cc

都是牛人 好好学习借鉴下

多谢多谢,回去查一下dff!^^

但还想请教一个问题,如果是dff有问题,为什么从测试结果上只能看到第一级对应的数字码部分由错误,而其它级对应的位置没有这个现象呢?最近思路有些混乱呀,麻烦啦~

你现在已经确定出是第一级的权重丢失了么?说明已经非常接近bug了,现在只要好好看电路便是。

我也仅仅猜测是dff,都要重新看仿真结果;你说得问题,举个例子,dff的setup时间刚刚满足,会不会因为芯片制造或是温度变化造成部分区域进入了较差的corner,然后setup就不满足了?当然了,到底是什么样子,我也不知道,所以必须要仔细仿真,看看能不能在仿真结果上重现测试中的现象。

嗯,通过测试已经可以确定是第一级输出出现了问题。还是想请教一下您,现在比较器阵列部分整体后仿总是不收敛,想在前仿中可不可以人为注入一下bubble这种现象,看看仿真结果是不是和测试一样呢?多谢多谢!:)

这个在matlab里更好做吧,用得到的数字码做处理就行了,virtuoso里可能montecarlo也仿不出来。但是这样的问题是,仍然不能100%确定是那的问题。

刚才又想了下,应该不是出了亚稳态,因为mdac的结果是对的,亚稳态是在比较器出结果的时候已经有了的。所以你还是查查后面的数字电路吧。

debug依旧无发现,又来请教前辈啦!

鉴于之前可能描述不够清楚,这里特意截了测试波形图,应该更直观啦。

图1频率较低,芯片正常工作(逻辑分析仪内部时钟采样,请忽略那些毛刺,芯片自己时钟采没有那些毛刺,也请忽略不标准的正弦,仪器受限)

图2 频率升高,开始出现转换 错误

图3再高一点。

图4再高一点

图5不能再高了。

情况呢就是这么个情况,还请各位牛人提点一下,不胜感激!

图1