第一次TAPEOUT的BANDGAP电路,工作不正常,请问可能是什么原因

怎么个不正常法?

BANDGAP REFERENCE 一般是不需要POST EXTRACTION 仿真的

会不会电流太大,金属太细?

你后仿真带着esdpad了吗

大侠,总电流大约在200uA左右,请问这样的情况,是不是任意的线用来连DIE和PACKAGE都可以呢?

没有呢,因为小弟没有经验,在电路上没有ESD的设计,只是在做WIRE BONDING的时候,以及在把整个PACKAGE放到面包板上的过程中,一直用一个ESD环在连着地和自己的手。请问这个会是问题吗?

看样子package和esd的问题

可能是ESD的问题,不只是你的手会放电。Package的设备也会

esd通常pad里面都有的,一般不会是这个问题。刚上电不正常,怎么不正常法啊?应该输出多少,实际输出多少?电流多大?

正常应该是输入2.5V,输出1.12V,输入电流大约200uA。我测试了好几个芯片,有两个情况

(1)有一个刚开始是1.12V,那时候没有测输入电流,后来就跳到1.8V了,电流就跑到了1,2mA左右了。(2)另外一个芯片没有输出,我测了一下一个内部接地的电阻的PIN,本来是80K左右的,但是测出来只有2,3K。不确定这个是制造的问题还是别的原因。

我想请问一下,(1)对于情况1,有没有可能是上电的时候,POWER SUPPLY本身的问题?(2)需要不需要在INPUT的地方加一个滤波电容之类的?如果是的话,大概要多少合适呢?(2)对于情况2,如果暂且相信制造的电阻差距没有那么大的话,有什么原因可能造成一个电阻值变小了那么多呢?如果做WIRE BONDING的时候,由于不熟练,在一个BOND PAD上重复了几次,会不会出现这个问题呢?

谢谢!

什么结构的bandgap?每个芯片的内部80k的电阻测出来都是2,3k么?最好上个电路图

It is a good example to test the circuit.

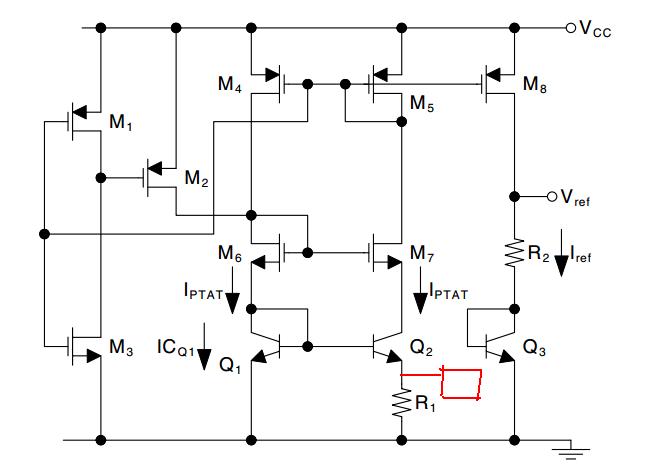

大侠您好,这是一个类似的电路图。这是一个电压模式的BGR,生成的PTAT电流流入一个DIODE-CONNECTED的三极管。R1就是我说的大约80K左右 的电阻,我在这里引出一个BOND PAD(红色的部分),发现工作不正常之后去测这个值,测出来只有2,3K。现在的问题就是样本太少,总共只有4个芯片,其中有三个工作不正常,然后这个地方的值也是从2,3K到30K左右,另外一个芯片因为WIRE BONDING的原因,这个PIN断了没有办法测。

不知道除了制造的原因之外,可能还有其余的原因会造成问题吗?谢谢!

疑问:1)为啥启动电路sense电流源的Gate?如果电压波动,启动电路会反复开启,出现周期性电流,造成PTAT不准确,VBG输出异常。

如果Sense的点是Vbg呢?会不会不出现这个现象?Vbg是具备PSR+能力的,建议你再加一个2P左右的电容降低噪声。

2)测试的电阻是啥类型?Poly电阻出现如此误差的话,建议你换工艺了。如果是diff电阻,你考虑了衬底电位嘛?

谢谢大侠指导!以下是回复:

(1)这个启动电路结构是从别人那里抄过来的,当时在别人的BGR上是可以工作的,我们只是拿过来重新做了LAYOUT。那么您的意思是在VCC和GND之间加一个2pF的电容来降低噪声,看看是否可以避免重复启动是吗?

(2)电阻确实是POLY,但是因为我们的WIRE BONDING是刚开始学着做,不知道会不会因为WIRE BONDING引入这样的问题,如果能排除WIRE BONDING的问题,那么只可能是工艺本身的缺陷了。不知道大侠对于WIRE BONDING可能引入的问题有没有什么指导呢?

1. ESD PAD

2. Start up circuit

3. Leakage

首先纠正一下,我不是大侠。再差的工艺poly也不至于从80k变到2k?

话说怎么只有四个?MPW一批最少也24pcs啊。

你测电阻可是你的电阻和管子的并联阻抗?

1)仿真看看启动的反相器工作在啥区域?是否存在两个管子都饱和的情况。

2)启动电压Sense Vbg,在Vbg端加2pF对地的滤波电容

3)面包板测试die,如果静电防护到位,可以先排除这种情况引起的问题。

4)VDD个GND之间最好多加一些稳压电容,毕竟你的VDD的Bonding是有2nH左右的电感。

ESD问题?

我们的芯片是蹭别人的,所以别人只给我们四个。

从电路图上来看不会吧,那个PIN和地之间只有那个电阻,而那个PIN到VCC之间应该算是无穷大了吧

谢谢大侠建议!有几个问题想再向您请教:2)启动电压Sense Vbg,在Vbg端加2pF对地的滤波电容

问题:您的意思是,在OUTPUT地方加上2pF的对地电容?

3)面包板测试die,如果静电防护到位,可以先排除这种情况引起的问题。

我们是把DIE BOND在CERAMIC PACKAGE上,像这样的PACKAGE(https://www.google.com/search?q=CER-DIP&source=lnms&tbm=isch&sa=X&ei=LpnFUvvGDMbNsQSAqIDgDQ&ved=0CAcQ_AUoAQ&biw=960&bih=472#facrc=_&imgdii=_&imgrc=i2eWNHmAl6bydM%3A%3BTo93-9-TdMmTLM%3Bhttp%253A%252F%252Fwww.topline.tv%252Fimages%252FCERDIP-SB-N.jpg%3Bhttp%253A%252F%252Fwww.topline.tv%252FCERDIP.html%3B114%3B123),然后放在一个ZIF SOCKET上(https://www.google.com/search?q=zif+socket&source=lnms&tbm=isch&sa=X&ei=TZnFUvzHG66gsQSD14HADA&sqi=2&ved=0CAcQ_AUoAQ&biw=960&bih=472#facrc=_&imgdii=_&imgrc=pHx1Snx1wfFtsM%3A%3B2FEPwS1vm0pgtM%3Bhttp%253A%252F%252Fwww.hobbytronics.co.za%252Fcontent%252Fimages%252Fthumbs%252F0002109.jpeg%3Bhttp%253A%252F%252Fwww.hobbytronics.co.za%252Fp%252F590%252Fzif-socket-28-pin-03%3B600%3B600),再把ZIF SOCKET放到面包板上。这样我除了操作的过程中,带上静电防护环,还有没有什么需要注意的呢?有时候我拿着面包板的时候,没有办法保证时刻手上都带着ESD防护环,因为需要把板子拿来拿去,请问这样可以吗?

4)VDD个GND之间最好多加一些稳压电容,毕竟你的VDD的Bonding是有2nH左右的电感。

您觉得加上10uF的输入电容是否足够呢?

1)Output对应Bandgap电源输出端

2)陶瓷封装+socket方案是可行的。片内ESD能力弱,一定注意测试操作,不要轻易触碰芯片管脚。尽可能排除ESD问题的引入。

3)VDD在片外加多大电容取决于你的输入电压源,可以用示波器测试一下输入电源电压是否抖动得厉害。通常加1~100uF的陶瓷/电解铝电容即可。

那个还真不一定是高阻哦!

内部80K电阻到地的节点测试出来只有2-3k可能是节点连接的栅极到地击穿了 产生部分电阻特性。

还是很有可能击穿了q2的eb极pn结。测出来30kohm那个结果的电流是多大?如果可以最好用台式万用表,加电流测电压。如果有图示仪可能效果更好一些。

不好意思哦我们没有这类作为电流源的仪器呢。如果真是EB节击穿的话,那应该说是ESD的问题吗?

。台表都没有?实验室怎么做实验呢?ESD问题的概率比较大,但不敢说死了。