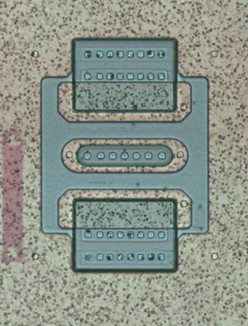

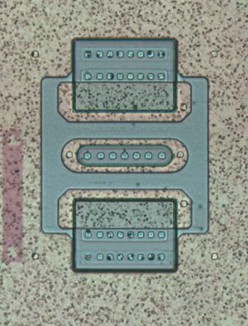

帮我看看这是神马器件的版图 谢谢啊

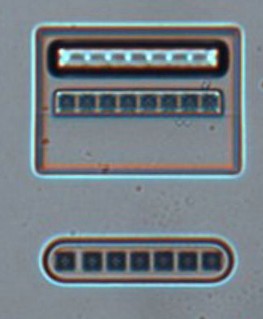

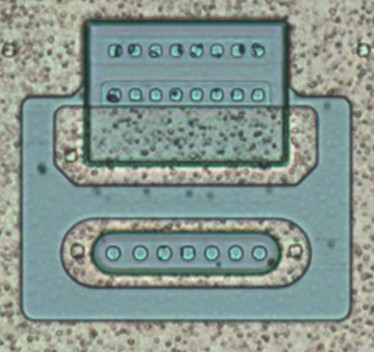

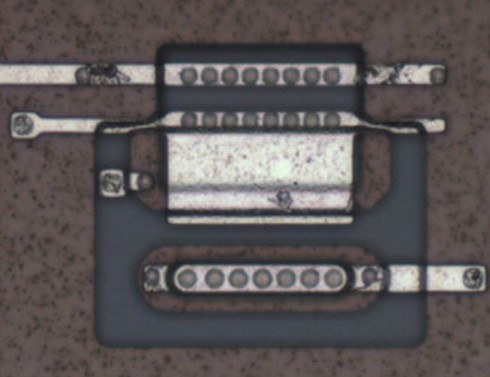

依次为染色层poly层M1M2

谢谢啊

貌似就是个DENMOS(Drain Extended NMOS),就是Vds可以高压的NMOS。当然也可能是PMOS,没有更多的信息去判断。

继续seeing

谢谢指点啊,但是源漏栅那些怎么确定呢?再次谢谢啦

应该是NPN吧,从下到上分别是C E B,其中E和B的位置还要根据电路再确认下

从覆盖的poly看应该是MOS。

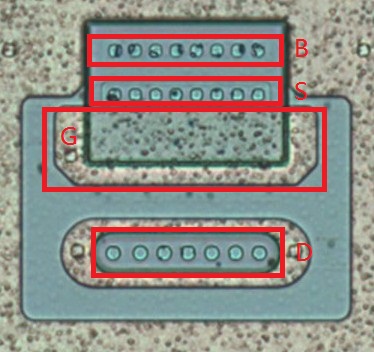

三排孔从上到下依次是B、S、D。中间poly是G

没看见poly引出的一端。如果是高压NMOS的话,衬底图片S与poly交叠那里没看见自对准的线啊;BUCK端接进有源区了,该接衬底才对;漏极应该有个HV_WELL的扩散吧。

小编,你这个是多少电压的芯片,poly那端接到什么地方?

gate poly的引线孔很明显啊。

B端不一定是衬底。如果是NMOS,S端和B端可能是做在NW里的PW里。

小编,管子周围的poly是连到地的还是连到电源的?

谢谢谢谢

该管子周围的poly是接到VDD的 啊,

另外请问栅上盖金属是干嘛的呢?

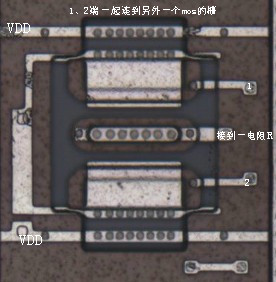

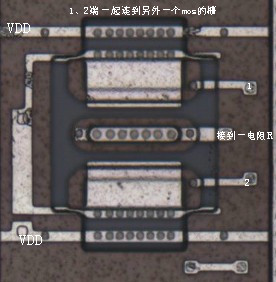

中间那一坨ploy最终接到了其他mos管的栅极,然后芯片电压最高在70v左右。那有必要做高压mos吗?

而且你描述的它的S最终链接到了其他mos的s或者D,这种栅链接其他栅,S链接其他D或者S是啥子意思啊?

旁边的poly接VDD,那么这个管子是PMOS管了。

gate上面盖S端的金属不知道是干什么的。

你说的这些连接当然有可能了,不奇怪啊。

B端是连接VDD的,S端可能连其他PMOS的D、S

一般 MOS 都是 5v3.3v ..

20~40vdual gate 會是 thick oxide , 這些MOS 畫法已有對稱

和非對稱的方式

至於 LDNMOS 一般都是 thin gate (就是低壓GATE但是drain 耐高壓 ) .

drain 拉開距離就可以 耐不同高壓, 20v30 40 5060v ..

不過 比較怪的是

圖上有兩端畫半圓方式 , 以前看過韓國代工廠60v BCD 是畫八角型方式 .

至於畫兩端畫半圓比較常在 bipolar process 看到

特別是平面bipolar 都會畫半圓或圓形 ,

如果 vertical bipolar 一般都畫類似 MOS 方方正正方式.

MOS 會看到 跑道方式 LAYOUT會是 500v700v UHV process .

這類會畫相當相當的大顆

樓主IC 編號多少 ?得看IC DATASHEET 吧.

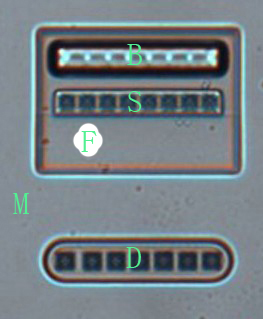

M就是这个管子的衬底吧,那么B为什么和S在同一F框里面呢;如果说这个F框才是MOS管的BUCK,那么D为什么不在这个BUCK里面呢?

还有,包围B和S的这个F框应该是有源区自对准留下来的,S和这个F有源区应该只有一条分割线,那就是有源区和poly交叠的那条线,其它地方应该是合并的,但在图上看S和有源区明显是两次注入。

下面贴个HV NMOS的图,可对比下

seeing

lt4320

谢谢你谢谢你

对比我的图2、3发现你说的B和M是有链接的(3金属1在2图中有孔),然后两者又一起链接到了VDD……这是不是说其实M和B 是一样的?你的意思是M点从衬底有CT接上来并和B连在一起吗?从图中能看到的是B与周围的poly是连一起的

恩恩我就是说B和周围的poly是链接一起的哈,,,不是M点我以为你M是指那圈poly呢嘻嘻

這是類似 同步整流方式須要 很大 driver 能力去推 nmos ,而且 nmos RDS 要低的話會很貴

, 以前使用過6ms9ms Rds_on mos .真的不便宜阿.

一般來說 bridge 多是 ac/dc很多都是 400v 起跳,我看到9V to 72V Operating Voltage Range

但看網頁

Applications- Security Cameras

- Terrestrial or Airborne Power Distribution Systems

- Power-over-Ethernet Powered Device with a Secondary Input

- Polarity-Agnostic Power Input

- Diode Bridge Replacement

可能是電壓低 但大瓦特如 48v大電流的 power over ethernet .

不是AC/ DC 使用 方式 .說真的換BRIDGE 取代DIODE 方式 當然可降低損耗但是 太貴,

一般 ac/dc 會輸出端併 schottkydiode 就是降低volt drop ,Vd=0.7直接改使用 schottkyvd=0.2~0.3

改使用MOS一般是~mv .得看 Rds * I

而且 很多FLYBACK 跟本沒有 使用 同步整流方式 , 因為只增加 1~2% 效率

花太多錢, 只有 拼 85% ~90% 那類高單價POWER SUPPLY才看過使用 同步整流方式. 一般都不使用 ,

不過 90v 應該是 LDMOS process ..

google linear tech 好像有 0.35um BCD .不過 不知道是否耐壓 90~100v .哇塞,真的很谢谢你的指点

这个芯片很新,它的研发价值我感觉也不是很明显……不过碰巧手头有这个的版图,就想提出来研究哈……结果发现里面很多器件不常见,就发出来请教下你们

芯片的频率datesheet上频率范围在DC to 600Hz,输入–3V to 80V,输出9V to 72V,您的意思是这个是耐高压的LDMOS之类?

再次感谢一般MOS PROCESS

0.5um5v

0.18um2.5~3.3v

耐高壓到 80~90v , 如果不是LDMOS

那 gate oxide 要多厚?連一般 外面POWER MOS4n60 .gate 也耐不到如此高

要耐80~ 100v都算UHV 類

500v~800v 是常見, 比較少100v125v..OKI有類似

但沒使用過.

當然還有 更高壓 , IGBT 有些 1000v这个应该是BCD工艺吧,BCD工艺不同的foundry差异很大,现在没有更多的信息,只能是推测了。

如果是P型DEMOS,你图中的M区域不是它的bulk,而是D端耐高压的漂移区。F是bulk(但是奇怪的是F是有源区掺杂形成的),B和S在F里面也就不奇怪了。

你说的S和F其他地方应该是合并的,这个不一定。

你重新截个图,把管子周围更大范围给大家看看。

回复 24# ygyg100

回复 24# ygyg100

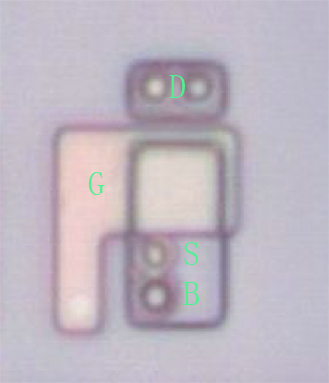

我查了下芯片数据,这是CMOS工艺,PL约1.7um……另外图中大量出现了共用你之前描述的D端的器件,如图 poly层和金属连接

回复 23# andy2000a

回复 23# andy2000a

我查了下芯片数据,这是CMOS工艺,PL约1.7um……另外图中大量出现了共用其中一端的器件,如图poly层和金属连接扩展漏端MOS

没有看懂是什么东西

回复 29# ystwyfe