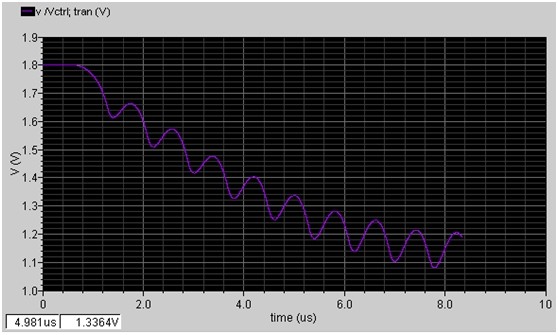

仿真一个锁相环的工艺角时,在ss情况下Vctrl会出现振荡情况

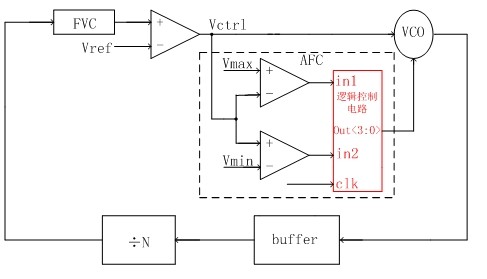

架构简单介绍下

AFC也是反馈控制的一部分,当然会有影响。

小编可以计算在振荡时,控制电路的输出值对应的 Kvco ,然后再验证phase margin

我觉得也有影响,但是不太会计算相位裕度(是仿真还是要手算呢),其实在仿真的时候Vctrl处还有一个大电容的,就是为了调节相位裕度,但是电容加很大以后结果还是振荡,不知道是不是我方法有问题?求解答。

http://bbs.eetop.cn/thread-240694-1-1.html

试试这个软件

软件看到了,对于pll是挺方便的,但是这个是FLL,而且环路里有一个小环路AFC,所以估计情况不太一样呢,不能直接应用吧?

用这个软件仿真phasenoise时,VCO噪声的.phn文件哪里来?

减幅震荡也是正常的,相位裕度余量足够就行。AFC工作在大信号状态,loop小信号工作应该设计成AFC工作以外。

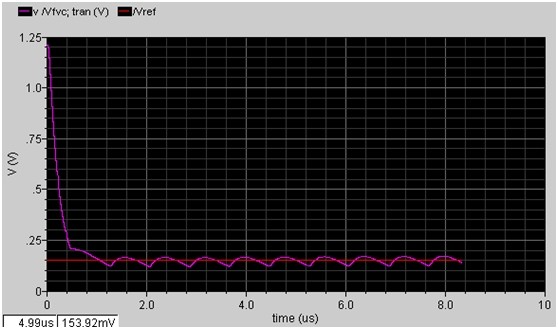

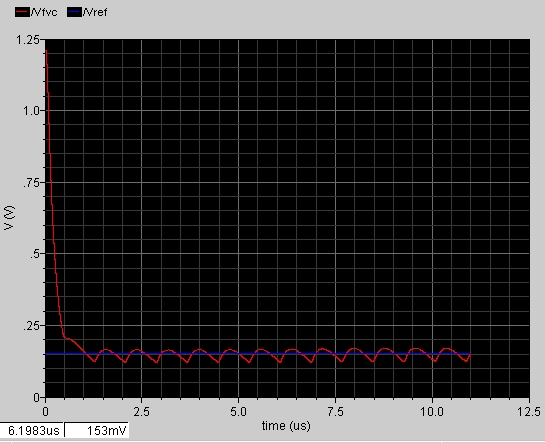

可否上传vtune和正负vref的瞬态波形

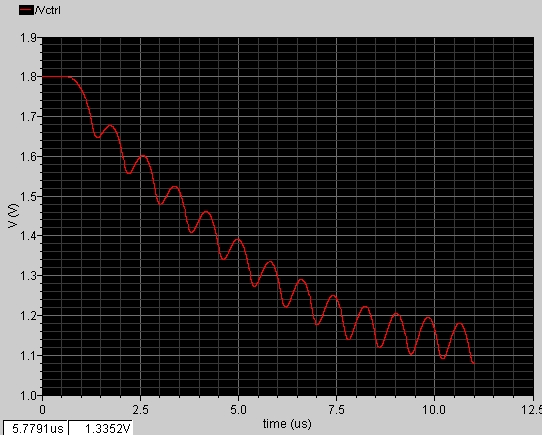

关键吧,不是减幅振荡,就是一直以某种固定频率振荡的。AFC大信号工作的话,是不是就不影响整个电路的稳定性了?出现图中这种情况也不知道什么原因。

你这是失锁还是相位裕度不够而振荡?锁定了吗?

afc断开,vco输入给一个合理的设置,先确定pll环路是否可以稳定工作

刚仿真了一下,断开之后,设置一个合理的vco值,然后竟然就行了,最后Vctrl又趋于稳定了,我可是什么参数都没改啊,只是断开了而已。看样子是AFC出现问题了吗?但究竟是什么原因呢?因为当出现振荡的时候,AFC明明也是按照我设定的递增递减工作的啊。

应该是没锁定吧。因为要是相位裕度不够的话,应该出现的是衰减振荡,可是仿真出来只是振荡了,没看出是要衰减的意思啊。

那稳定了之后,是不是表示AFC出问题了?

考察kvco极性,确定afc工作时环路是否是negetive feedback

你这么一说,我看了一下仿真结果,发现mimcaps_max/res_max/ss情况下,Vctrl是从Vdd往下降的,也就是说Kvco是负的,这样加上FVC的负极性,整个环路就处于正反馈了。怪不得会振荡。

但是这么一来有个问题,因为不同工艺角下,Vctrl的变化情况是不得而知的。那我怎么才能确保整个环路的负反馈呢?

错了,好像不应该从Vctrl的大小趋势来分析。因为当把AFC断开,环路正常工作时,Vctrl也是从大往小变的。Kvco和这个没关系。应该是和选择的调谐曲线的Kvco有关,那我再分析一下啊。

不知道该如何分析了,看Kvco的极性主要是从什么方面看呢?因为按照我对锁相环的理解,感觉连接方式是对的啊。苦恼中。

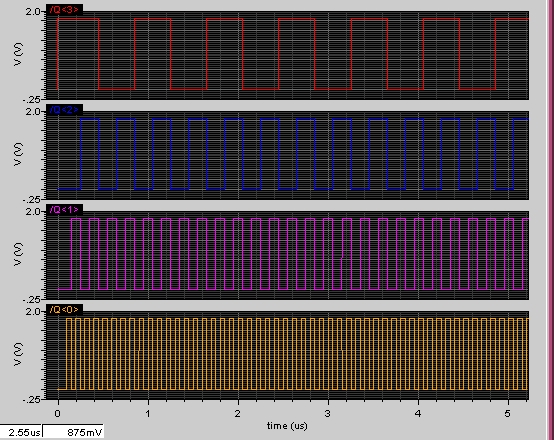

你这个是FLL如果没搞定,可以同时给出fvc、vtune、afc控制字输出、vco振荡频率。这样可以帮你分析原因

恩。是FLL。因为周围没人做这个,自己实在是想不出来问题出在哪了。Q3是高位,Q0是低位。Q3Q2Q1Q0=1111时,对应最高频率。因为Vctrl最后出现振荡了,所以输出频率也是一直振荡的。本来想要的目标频率是433MHz的。麻烦你了。感激不尽啊。

可不可以留个qq号啊?这样问问题比较方便,要是不方便的话,也没关系。在这上面解答也可以。谢谢啦

问题已经解决了,哈哈,谢谢你的回答啦。我把仿真时间clk改了一下。