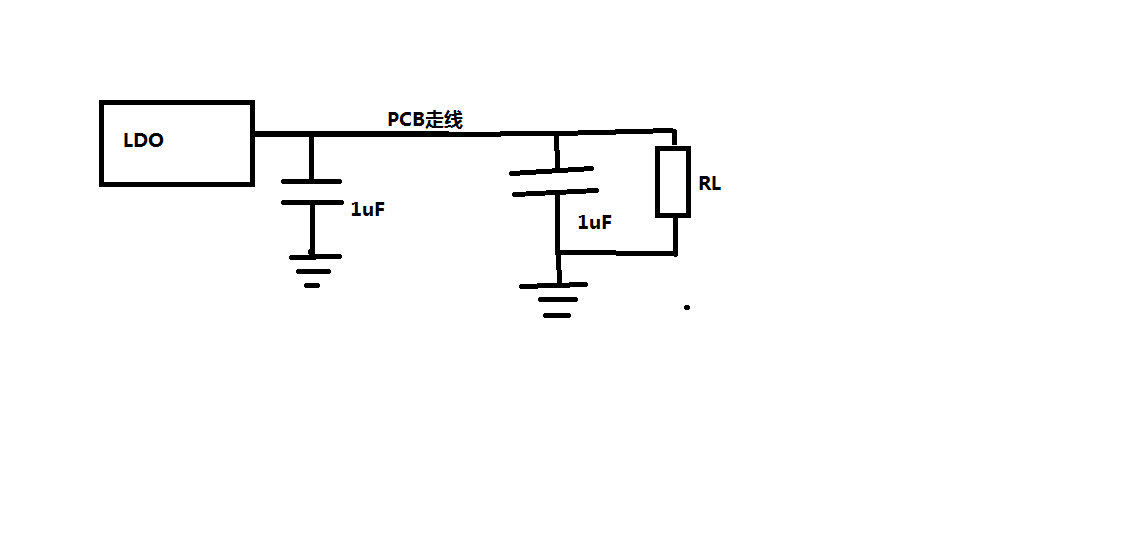

PCB寄生电感对LDO稳定性的影响

除非重新设计,否则再把电容移回去

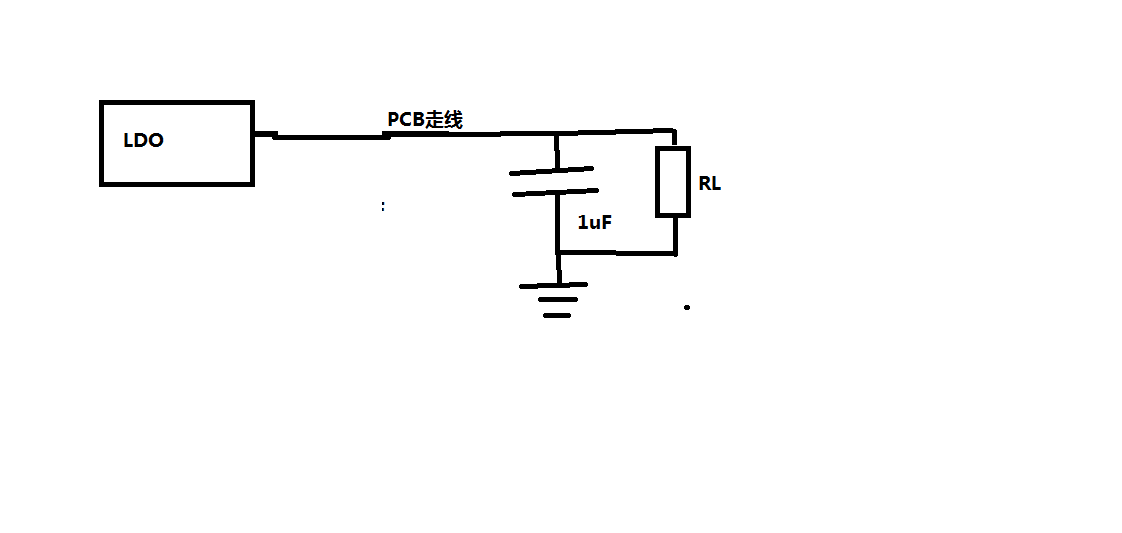

要降低成本,只能把这个电容拿掉,保留负载端的电容。只能重新设计了。可是,目前我只能想到通过压低LDO带宽,把寄生电感所引入的零点置于带宽外。有没有更好的思路呢?请指教!

外接Cap的LDO 对PCB走线没有这么敏感吧?

你设计的带宽多大?

PCB走了多长的线?为何不把负载的电容移到LDO输出的位置,你的负载是什么东西?

PMU芯片,给基带供电,走线长度大约50mm/0.2mm,这个长度没法再缩小了。

PMU芯片,给基带供电,走线长度大约50mm/0.2mm,这个PCB走线长度没法再缩小了。

LDO带宽大概1.8MHz左右吧,PCB走线50mm/0.2mm,根据PCB工程师提供的寄生参数,这么长的走线引入了20nH左右的ESL,200m左右的ESR。

PMU模块电流突变会在20nH电感上引起瞬间高压电压,这个高压不高于PMU的耐压就好,但要注意latch up。输出电容稳在靠近PMU,不会有上述问题,但是你LDO在重载时会由于寄生而振荡。这个你可以权衡下:要知道PMU的最大电流变化率,PMU的最大耐压,放电容于PUM和LDO的不同位置,以同时满足两者(仿真验证)不行。就改电路吧。

去掉近端电容测试,重载下输出震荡,重新设计电路是必须的了。那看来只能通过压缩LDO带宽来规避ESL的影响了?

5cm走线是长了点!Cap需要靠近芯片。一般也就几个mm以内

求问 pm是功率因数的意思么?

你LDO最大负载多大?降带宽把。

.......那玩意不是pf么.......

PMU芯片里面总共将近20个LDO吧,某些走线可以比较短,但是有些走线得绕,最长的就有5cm了...

Phase Margin,相位裕度的意思.

最大负载300mA,目前看来只能降低带宽了。

外接电容可以尝试不同ESR的Cap,看看有什么效果

300mA,你降带宽也不容易。

标题

pcb上的trace走粗一点,300mA走8mil有点细了,如果允许的话走线宽一点,电感就小一些

增加线宽对降低电感估计作用不大

嗯,作用小

陶瓷电容,ESR变也变不了哪儿去!

从PCB工程师提供给我的寄生参数来看,增加线宽对改善寄生L还是有一些效果的。

恩,你说的确实是的,从PCB工程师提供的寄生参数来看,线宽一些,寄生L确实能够小一些。

呵呵,这是个物理学基本的常识,自感与长度成正比,与线径成反比。

给点参数吧,我想看看不同宽度,电感差多少

你可以随便找个计算器算算,看看根据常识L和w是不是成反比

标题

对于简单导体,电感应该是和半径的对数成反比,但是传输线就有点不同

我记得以前算过bonding wire的电感,0.8mil, 0.9mil, 1mil 自感是越粗的越小,虽然差别比较小,但是pcb上走线可以走宽一点还是可以明显减小电感的

是有效果,但作用小,你计算下就知道。