急!毕设求助(增益自举运放侧键建立时间产生震荡了)

时间:10-02

整理:3721RD

点击:

rt,快答辩了,增益自举运放测建立时间产生震荡了,不知什么原因

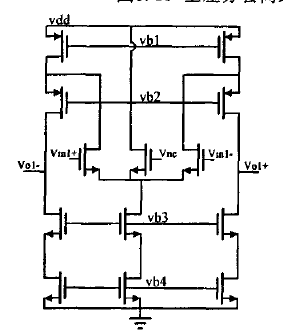

主运放和辅助运放都是折叠式共源共栅级的结构

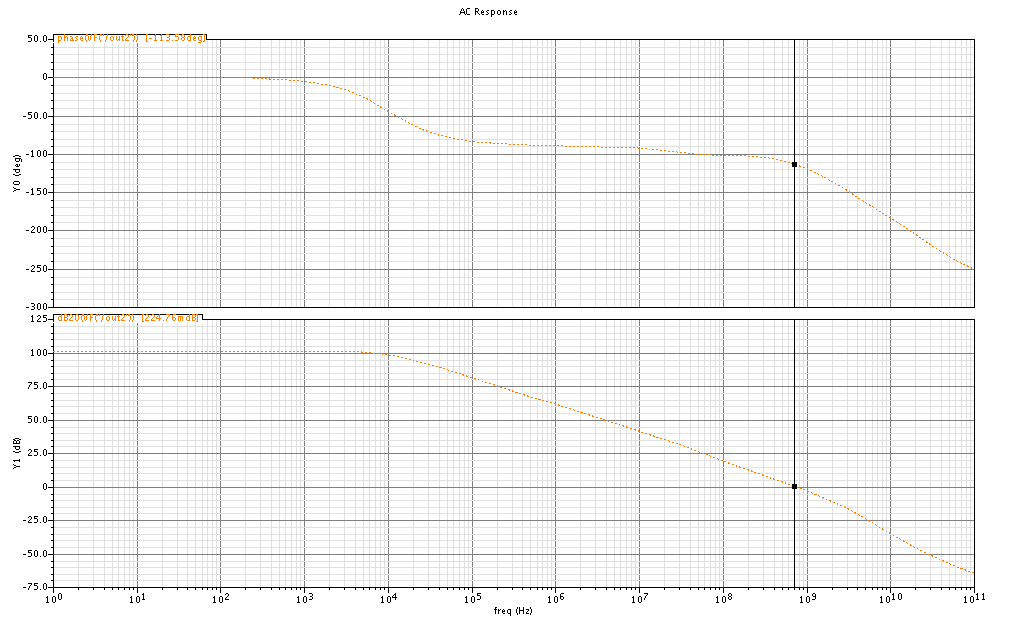

主运放和辅助运放都是折叠式共源共栅级的结构闭环增益约为100db,UGB约为740Mhz

开环UGB为820Mhz左右

运放的闭环增益和相位裕度

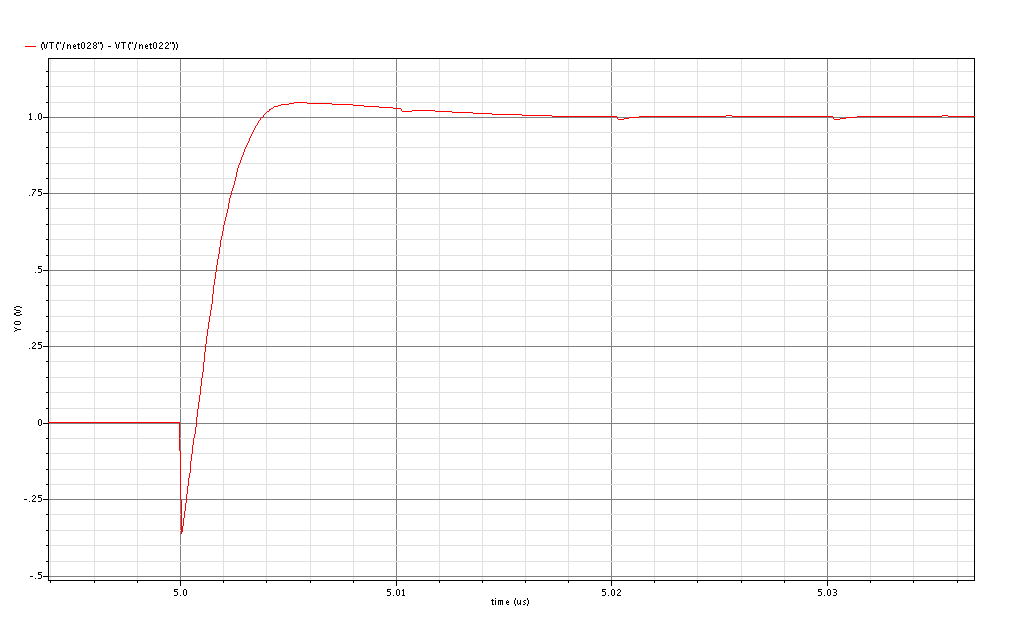

接成单位增益负反馈时测得的建立时间(产生震荡了)

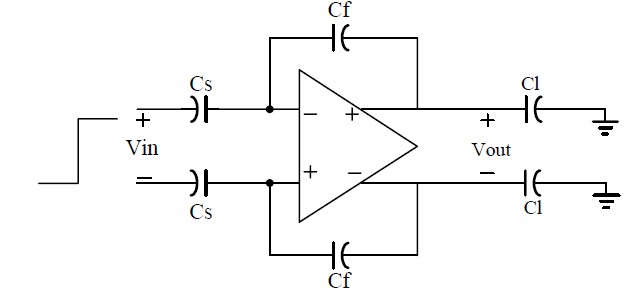

测试电路

自顶!

自顶!1

自顶!1

帮你顶一下~~

高手都不上坛子了吗

我看看,貌似有点熟悉

你两个辅助运放的UGB是多大?看看bult的那篇文章啊(你的闭环增益有100db啊。)

小编,你好,我现在在学习这种运放的做法,但是在辅助运放那块我碰到了问题(就是提高增益的运放),主运放和辅助运放也都是采用折叠式CASCODE结构,在辅助运放的时候

希望小编回应我一下,真的很感谢,感谢!