DAC的输出采样点的问题。急求。

1.对输出波形进行采样,如果采样在正好有glitch的部分不是SFDR很差吗?那如果采样在setting好一段时间的部分,SFDR不就好了吗?那我们做FFT的部分采样点到底应该在哪里啊?

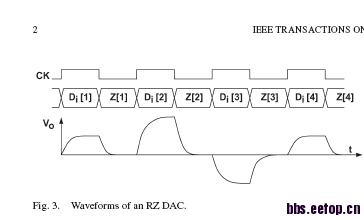

2.paper中提到的RZ的输出,如下图:

一半有数据,一般无数据,那我们在有数据的哪一部分采样啊?中心点吗?不同的点采样计算出的SFDR应该都不同吧?

一半有数据,一般无数据,那我们在有数据的哪一部分采样啊?中心点吗?不同的点采样计算出的SFDR应该都不同吧?还有就是对于RZ的输出,如何将其变为模拟信号啊?中间有一半周期为0呀?

忘热心人解答.....

很多种dac输出的模拟信号l连续时间都要用,加所谓的smooth filter,这个时候对毛刺有严格要求。

不知你所说的是何种应用。若是每个周期只采一个点,时钟能否调延迟避开毛刺?

还有请教你RZ类型的优点是什么?

paper上说是减少了harmonic啊,我想是的吧。个人觉得应该取到毛刺的点,这样做出的DFT才正确。是不是啊?

做DFT分析当然应该取到settling好的点出来的结果才比较好一些啊

作为dac应用,默认就是输出信号是连续的,所以一个周期采一个点是不对的,必须采足够的点才行。这和ad的情况完全不同。

1、第一个问题

对DAC输出做DFT需要分两步,每一步做出来的频谱要学会正确解释它的含义:

(1)每一个时钟周期做一个点,这个点应该位于“自己”认为最稳定的地方。这样得到的频谱可以用于解释幅度域的信息,包括:输出电阻、失配等等信息。注意:这个频谱不是真实的DAC输出频谱,差别很大;

(2)每一个时钟周期做2^n个点(n具体多少取决于器件特征频率,采样频率,带宽等,一般原则是越大越好),这样得到的频率就将DAC输出的所有信息就都采出来了,这个DFT频谱就与实际输出接近了。

2、第二个问题

RZ不是指码字为零,而是指输出两端电流或电压相等,从而差分输出为零。为了实现差分零,只需要p端开关所有码字之和=n端开关所有码字之和 就行了。

对于高速DAC,由于输出稳定需要很长时间,所以下一时刻幅度会收到上一时刻幅度影响,从而产生码相关效应。RZ可以减小这种效应,从而减小谐波。

我后来看了DFT的相关意义,明白了,做DFT一定要取很多点,不能只取一个,由于采样时间短,这样FCLK就大,做出的频谱更加接近analog的频谱,所以取一个点是不对的。

关于RZ的含义,谢谢解答,明白了。其实可以控制输出的占空比,让zero的空间小点,这样通过LPF的power就会大些。

我后来看了DFT的相关意义,明白了,做DFT一定要取很多点,不能只取一个,由于采样时间短,这样FCLK就大,做出的频谱更加接近analog的频谱,所以取一个点是不对的。

关于RZ的含义,谢谢解答,明白了。其实可以控制输出的占空比,让zero的空间小点,这样通过LPF的power就会大些。

那敢问DRRZ又是什么意思呢?

DAC的输出是由台阶构成的,做DFT分析不能只对一个台阶采样一个点吗?是要采样很多个点吗?一个台阶一般去多少个点