pipeline ADC 采样时序的困惑

时间:10-02

整理:3721RD

点击:

设计pipelineADC时,SHA和MDAC的采样保持时序,前仿真结果看起来很好,但是后仿却一塌糊涂;

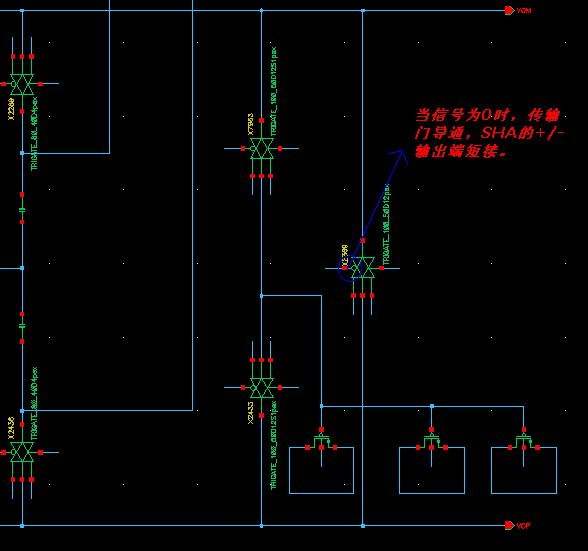

上图是SHA的输出控制,当图中的蓝色控制时钟为0时,SHA的输出短接

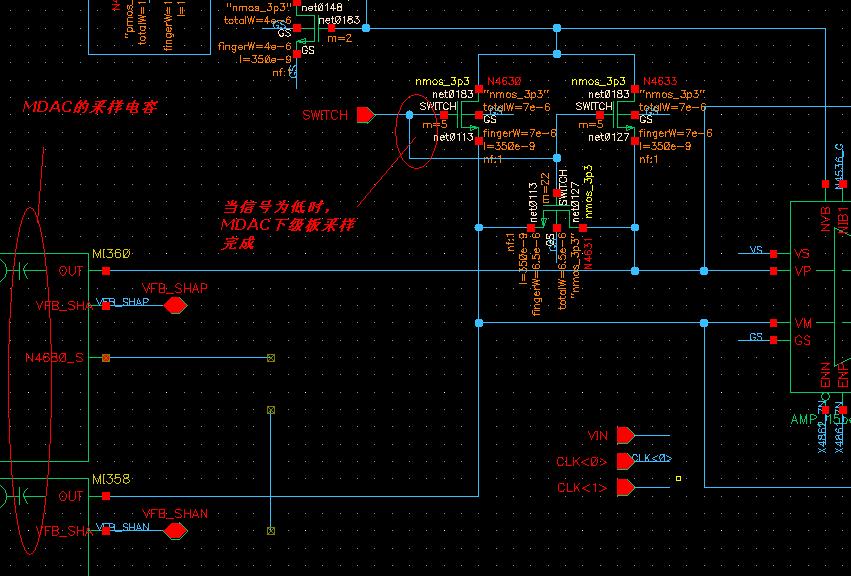

上图是SHA之后的MDAC采样电路,当图中的红色控制时钟为0时,MDAC对SHA的下极板采样结束。

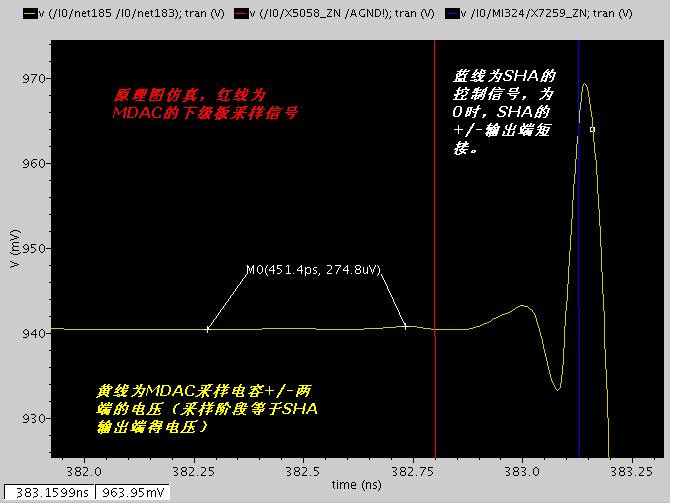

上图是前仿真结果,图中,红色信号为MDAC的下极板采样信号,蓝色信号为SHA的输出短接控制信号,黄色曲线为MDAC采样电容的上极板电压之差(也即SHA的输出差分电压)。

可以看到,蓝色控制信号的下降沿比红色的MDAC下极板采样控制信号延迟0.3ns,保证了下极板采样时序的正确性;当红色信号下降到940mV时,采样的信号波动幅度约为274.8uV,这是不是可以理解为时钟馈通和电荷分配的影响?

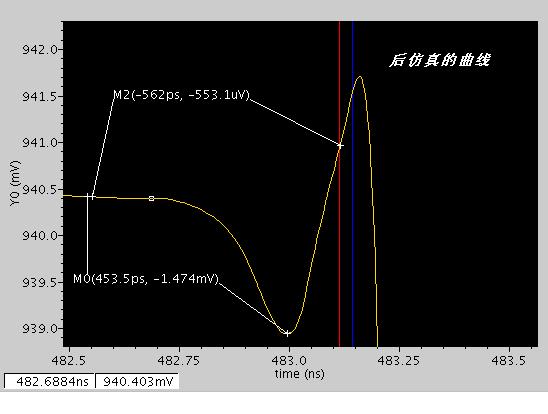

上图是后仿真曲线,可以看到,红色的控制信号几乎和蓝色的控制信号一起下降,延时也只有30ps左右(是不是没有了下极板采样的作用?);同时,MDAC采样电容的电压(黄色曲线)在红色信号下降时,剧烈的波动,幅度有1.474mV,这采样的结果正确吗?

求大神们帮我分析分析这种现象,后仿和前仿的时序差别太大了,这种后仿的时序图是否错误?感谢感谢。

也不知道描述清楚没,请各位大神帮我分析下,感激不尽

前仿的采样时序很好,后仿得太烂了,不知各位高人都是怎样验证后仿版图的采样时序的?如何判断后仿的时序也是满足要求的?

我估计是这两个时钟在版图上的走线长度相差太多,导致本应提前关断的时钟明显滞后了,先确认刚从时钟发生模块出来后的时序,如果时序没问题那就可以肯定了

刚从时钟模块出来的时序没有问题。我的版图是参照老外的片子画的,后仿时序出来居然是这个样子。但是,做整体后仿真时,SFDR比前仿也就差了3个dBc,真不知道是为什么?