LCVCO相噪仿真的问题:

LCVCO相噪仿真的问题:

最近在做PLL,VCO花了我不少时间,设计到最后发现个问题,实在没办法搞定,特贴出来求助!希望遇到过这情况的能给个不帮助,先谢了!

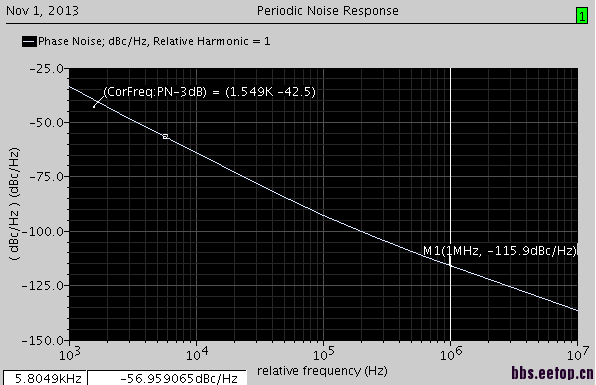

我做的LCVCO 中心频率是2.4G(调谐范围为2.3-2.5G),1.8V电压供电,希望在仿真时,在1MHz偏频出,相噪<-115dBc/Hz。现在在做PSS和Pnoise仿真时发现个问题:

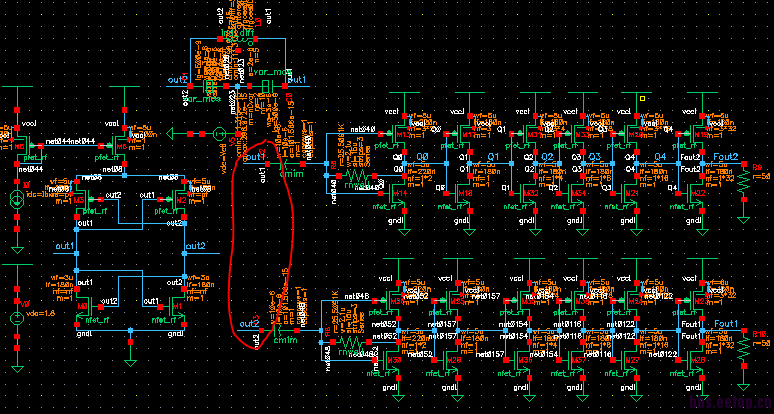

原理图如下

图(1)VCO带Buffer

在带Buffer的情况下,相噪曲线为:

图(2)VCO带Buffer的PN曲线

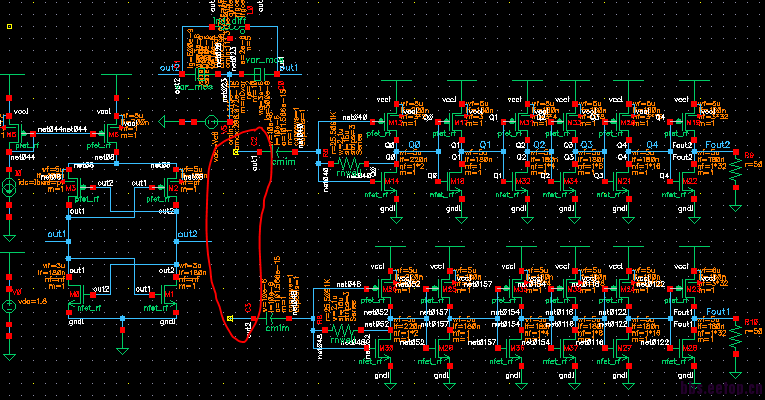

若我将原理图(1)中的buffer与VCO断开连接

图(3)VCO断开Buffer

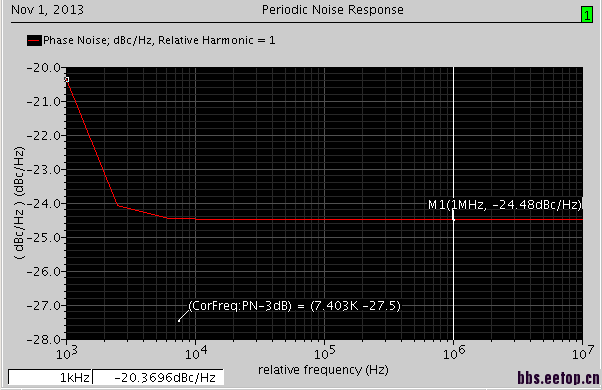

在断开Buffer的情况下,相噪曲线为:

图(4)VCO断开Buffer的PN曲线

问题:图(4)让我很不解,为啥不带Buffer的情况下相噪会变平了?还有就是我在图(1)VCO后面(buffer前面,即Lable--out1)接SAFF的二分频器,PN的相噪曲线和图(4)一样!很不解的问题,希望得到大家的帮助!

检查PNOISE的输出设置是否有问题。

谢谢你的提醒。我两幅图都是从VCO的输出看的,PSS和Pnoise的设置是一样的。

把后面的INVERTER先删去仿下试试看。

有时候仿真会出现些怪异的现象。

how about the osc freq without buf? Is it a lot difference ?

If you have div by 2, you need set the beat freq in pass to the half value of Vco, and observe the relative 2 content

应该是仿真工具的问题,PSS/Pnoise仿真容易得到错误的结论,不像TRAN仿真那样。

这是我的理解。

经常会很诡异的出现问题!后来有人告诉我 在二分频器放进电路中,用PSS仿真是不准确的。所以我现在二分频加进去后就不仿PN了!

你的理解显然错了,没有pss,pnoise analog设计的门槛不知道比现在要高多少

这个是!不过现在2分频器加入电路后的PN有点离谱(即使把2分频器加到Buffer的后面)!不知是我设计问题,还是PSS+Pnoise仿真算法问题!我觉得应该有人仿过吧,不知大家是如何理解的!

没看到什么离谱的,,,,多考虑考虑noise folding, am removal, 你就不觉得离谱了,当然分频比很高的时候converge还是有难度的

如果你加上二分频电路的话,PSS的基频应该估计为fvco/2,可能是这个问题导致的

我也是这么觉得!那我带负载应该如何仿真,是不是直接提取二分频的输入阻抗,然后直接用输入阻抗代替二分频来仿真?

两种方法,按理说你的VCO输出应该有buffer,所以可以拿掉divider,直接仿pss;或者你按fvco/2估计基频,然后在结果里看二次谐波量