模拟电平选择求问

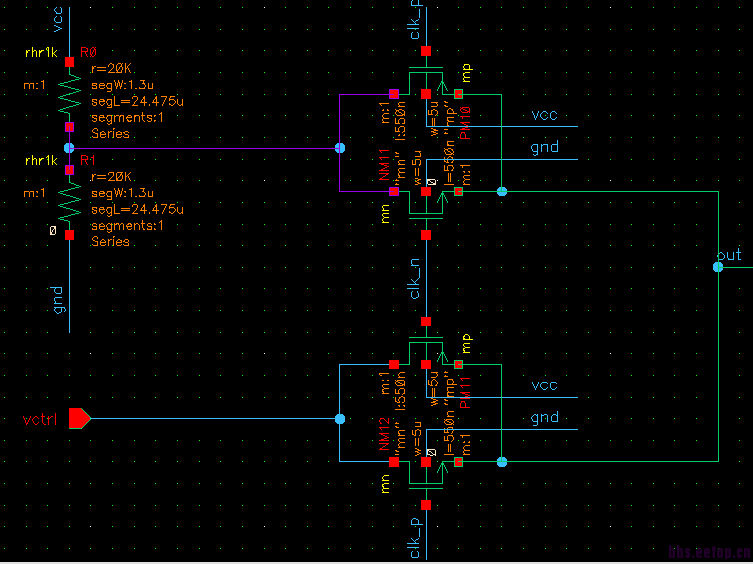

用普通的传输门结构做了一个模拟电平选择结构。如图所示,通过时钟的高低电平切换选择是内部电阻分压得到的2.5V还是外面芯片的输入电平(仅在芯片上电的时候的切换一次)。现在的问题是对于下面的传输门在刚上电的时候PMOS衬底的电压为0V,如果芯片输入VCTRL在芯片上电之前已经建立的话,这个PMOS衬底PN结就导通了,芯片存在烧坏的风险。不知道有没有什么好的方法解决这个问题,另外out端需不需要加个电容呢(out直接接到mos管的栅极上,输入阻抗应该比较大)?不知道大家都怎么实现芯片内部电平切换的?

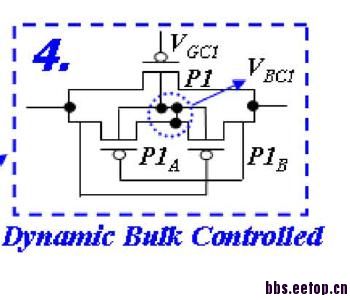

pmos 衬底问题:1用衬底选择电路选择最高电平。2衬源接一起。

输出要加电容。

这个问题是在上电过程中才会出现的。由于芯片还没有完全上电,如何选择电平呢?对于传输管源漏可能互换,衬源短接似乎也不大可行。另外,输出端本身就具有一定的寄生电容,加电容的原因是?多谢~

衬底选择电路自己找下,电容稳压。

OUT脚还是加个电容滤下波把,毕竟会有噪声的。衬底选择见下图:

查了一下,一般的衬底选择电路用在电荷泵等电路最高电平不确定的场合,但对于上电过程的应用似乎很少涉及。不知能否提供相关问题的资料?另外输出电容多大合适呢,有没有经验值还是仿真确定? 另外能想到的一个方法是在外部电平输入端串联一个电阻限流,不知是否可行?

衬底选择电路对于上电过程没问题,别老是听别人说,你自己想想啊。有没有问题你分析下啊!

做这行关键要有分析问题解决问题的能力,否则别干这个了,还有收集信息筛选信息,及快速的学习能力。这个是要锻炼,提高的。否则。

不好意思,纠缠太多了。但我相信该问题在设计中是个经常遇到的问题,在电荷泵等结构中衬底选择电路确实用得很多,但在衬底选择电路的资料中都没有提到将其应用在上电过程中,这点比较纳闷。不管如何,谢谢了~

能不能用是看会不会出现问题,要判断出不出现问题是靠你分析,和仿真。那你说它为什么在上电后能用?上电后用一定不会出现问题?你好好想想。我后来懒得回答,是因为有些地方你不思考就问,我对此比较反感。

而且经过自己思考和验证的东西才算是掌握的,千万别做:别人怎么说你就怎么认为的人。

我相信在电荷泵等应用中衬底选择电路的应用已经达成共识。但在电平选择器的上电过程中存在的衬底漏电问题(事实上也只是输入在电源上电之前建立才会出现,且需要输入驱动能力较强)上却找不到相关的资料,但这个问题又确实是存在的。之所以纠结这个问题,不是因为衬底选择电路在此处是否可用的问题,而是为什么大家不考虑上电过程PMOS管漏电?

LZ应用环境是什么呢,VCC和Vctrl 上电顺序 是确定的呢 还是 不确定的

你需要让人带你几年

你讲的都对,只是在这个问题上是不是可以针对这个问题直接告诉我解决方案呢(如果知道的话),我相信论坛也是个学习的路径,不是么?无论如何,还是多谢,如果觉得太烦,请无视。

应用中可能输入先上电的,所以要考虑这个问题。

这个问题 画个 纵向陪面图 就能分析 是不是存在 漏电的地方了

多谢关注,理论分析确实是存在的,因为该问题只在上电过程存在,并且输入的驱动能力一般没那么强,芯片直接击穿的可能性不大,但可靠性问题还是存在的。

理论分析确实是存在的?为什么呢?

可以用图示来讨论一下

假设芯片上电之前输入端Vctrl=3V,PMOS管衬底接VCC,在上电初始VCC电压为0V,这样该PMOS管衬底(N阱)和输入端Vctrl(p型)之间的PN结正向偏置,存在漏电。当然芯片上电之后由于衬底已经处于最高电平,漏电问题不会存在。

为什么不将vctr1直接连到分压电阻的分压点那,这样就没有那些问题了,当你不加vctr1时(可以外挂一个电容)为分压,加vctr1时为vctr1.

由于需要芯片内部切换电平,所以不能用该方法。