设计DAC,如何加快响应速度?

时间:10-02

整理:3721RD

点击:

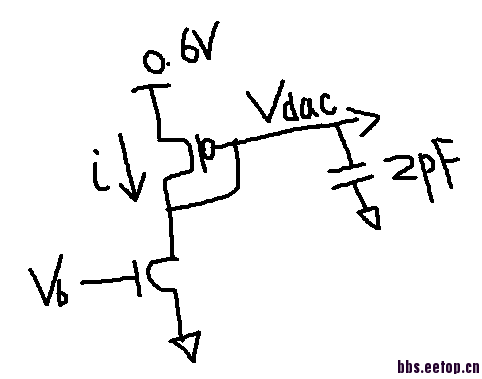

现在设计一个亚阈值区的DAC,原理大概就是下面的图,电流 i 想要从300nA变到20nA,但输出线上负载较大,又是亚阈值电流,所以Vdac建立得很慢(从大约160mV到300mV,需要10us以上),有没有什么好的解决方法,最好建立时间能到1us内?

试过在Vdac上加一个预充电的PMOS,给一个窄的负脉冲栅压,把Vdac往上拉一拉,但这个很不准,受PVT影响太大了

真的没人知道?不算很难吧

I think the only way is to reduce the loading capacitor or increase the gm of the PMOS

是寄生电容,减减不了多少

试试再加强一些PMOS吧

应该有比较技巧性的方法吧,只是我想不出

加一个运放来驱动寄生电容吧。要不无解

具体怎样加法?0.6V的运放会不会设计很困难啊