LDO误差放大器环路不稳定

LDO中误差放大器反馈回来环路不稳定,一般要怎么解决。误差放大器的增益一般又是多少呢,求经验大牛指导。放大器用的最简单的一级差分输入单输出的OTA,是INTERNAL compensation。

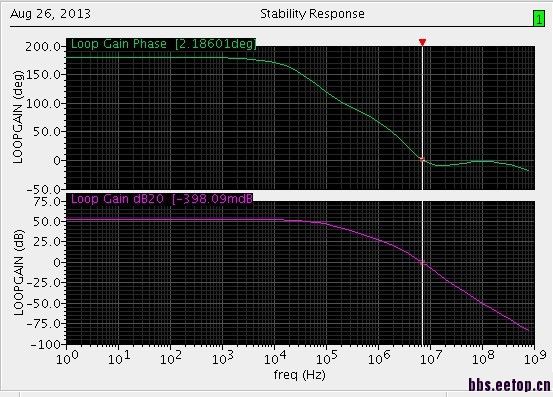

LDO中误差放大器反馈回来环路不稳定,一般要怎么解决。误差放大器的增益一般又是多少呢,求经验大牛指导。放大器用的最简单的一级差分输入单输出的OTA,是INTERNAL compensation。增益大概52dB,gain phase急剧下降到零左右了

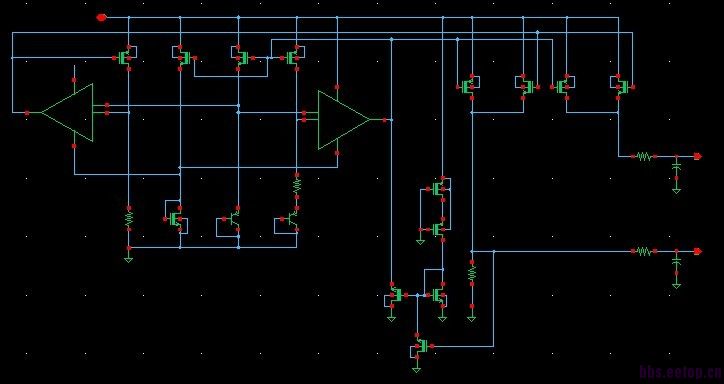

請把你的LDO電路圖 秀出來

LDO架構很多

需求不同(HIGH PSRR,fast transient,ESR+off chip capacitor,on chip capacitor)

如果需要Line/Load Regulation,DC PSRR,那ERROR AMPLIFIER DC GAIN越高越好

LOOP UNSTABLE,就要弄個ZERO或其他方式來增加PHASE MARGIN

不曉得你的架構

故無法回答

图已经补上,在90nm工艺下性能可以,新人公司要求用55nm工艺,发现增益小,环路不稳定,应该从哪方面入手呢

我看起來

左邊是LDO error amplifier+ output stage(pmos + feedback resistor)

中間是Bandgap loop

在右邊是startup circuit

最右邊openloop output stage

有說錯請指正

另外

左邊第一顆OP是one stage op或two stage op

這顆LDO是INTERNAL compensation嗎?

這樣才能繼續討論下去

用的一级OTA,是INTERNAL compensation

Error amplifier是一級op,跟output stage合起來是兩級

兩級CLOSED LOOP主極點都常都設在第一級輸出,

那你就在error amplifier output跟VDD之間加個COMPENSATION CAPACITOR

值越大

LOOP的PHASE MARGIN越大

另外DC GAIN太小

請把ERROR AMPLIFIER的MOS的LENGTH加大

若還不夠可考慮FOLDED CASCODE

DC GAIN大小跟LOOP的PHASE MARGIN沒有因果關係

GBW跟SECOND POLE之間的倍率才跟LOOP的PHASE MARGIN有因果關係

谢谢,我去试试

至少给出bode plot吧

图片上了,周末找不到所以周一才发

相位裕度还有什么方法调整一下吗,增益到了50多点,图已经贴上了

相位裕度有点低吧