如何提高流水线ADC的运放的建立时间?

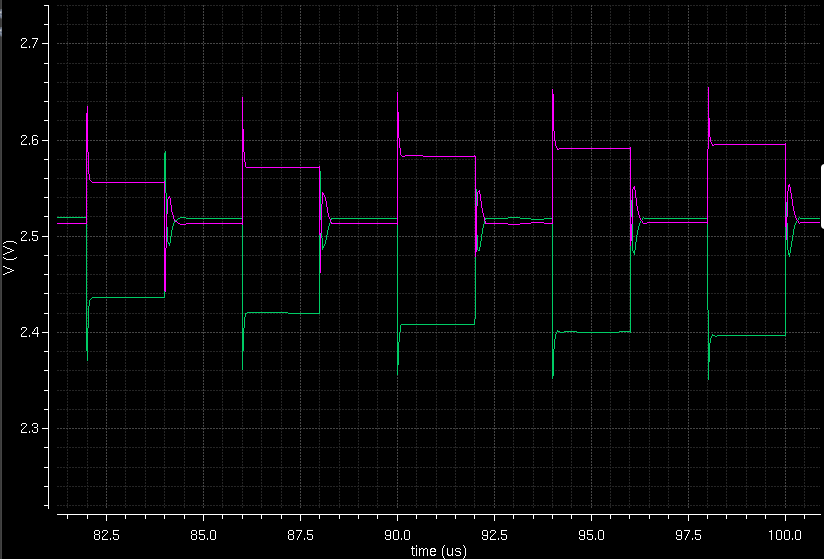

把运放用在MDAC中,发现开关电容电路的建立时间很慢,如下图,上升下降时间大概8ns(SR=20V/us),建立时间需要100ns,并且建立过程中有很大的过冲,请问这个过冲如何消除,如何进一步减小建立时间?

谢谢!

下图是MDAC的输出波形

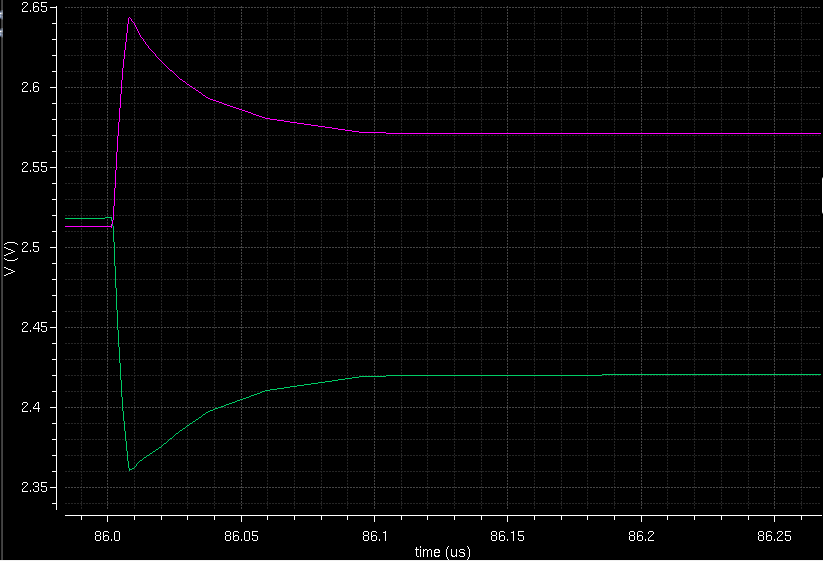

下图是建立过程的细节,有一个大过冲

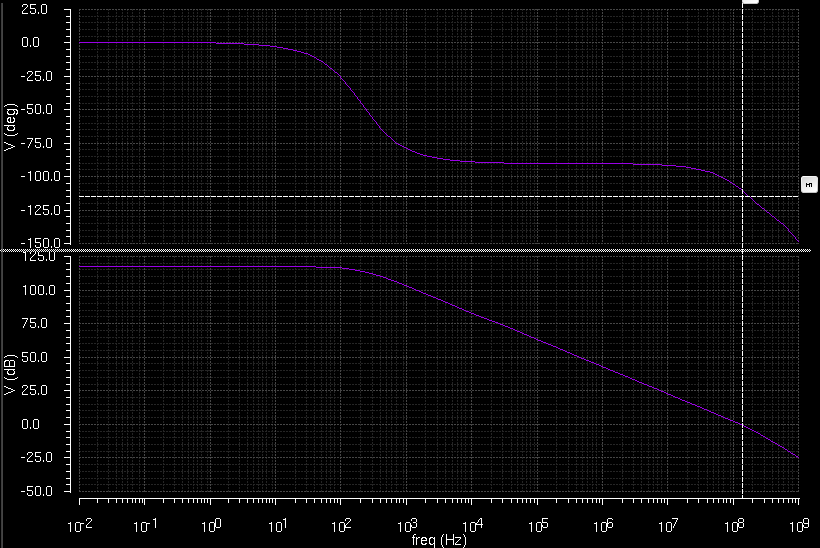

下图是运放的波特图

無missing code的條件下,residue amplifier的輸出誤差必須小於(<)1/2^10,先不考慮電容誤差:

1.op finite gain error佔 0.125lsb =>1/(AB)=1/(2^10)/4 -> A>2^(10+2+3)=32768,約90dB

2.settling error佔 0.5lsb => e^(-Tset/tau)<1/(2^10)/2 -> tau=Tset/11/ln(2),

Tset代表最多可容許的settling time,假設有40ns,可得到residue amplifier的-3db bandwith為

1/2/pi/tau約30.4Mhz,單增益帶寬=30.4Mhz*8=243.2Mhz

增益足夠,但帶寬不足,僅供參考!

谢谢,我的带宽是160MHz,还是不够是吧,我再试试增加一些。

在MDAC中,Cs=3pF,Cf=1pF,下级MDAC也是2.5级,那么请问在仿真运放时负载电容是选择5pF(Cf+Cf+Cs),还是8pF(Cs+Cf+Cs+Cf)?

增益这么大,开环BW过小吧。

設op輸入端對地等效電容Cip,運放等效電容如下:

(Cs+Cip)*Cf/(Cs+Cip+Cf) + Cs,

下級電容不需用到3pF,1pF應該足夠!

请问你的单位增益带宽计算时为什么乘了8?

很直覺的把residue amplifier的gain當成8(把Cl看成Ci),應該是4倍才對,

那合乎規格!

第一级Cs=3pF,Cf=1pF,第二级Cs2=1pF

先忽略Cip,那么计算得到 3*1/(3+1)+1=7/4pF,这样计算对吗?

哦,那速度慢是因为仿真时负载电容5pF选择的太大, 根据你的公式,我试试7/4pF

请问,如果运放接成buffer形式,单位增益负反馈,这样这样算出来-3dB带宽不就是运放的GBW吗?