关于2.5bitMDAC中比较器的结构选择问题

时间:10-02

整理:3721RD

点击:

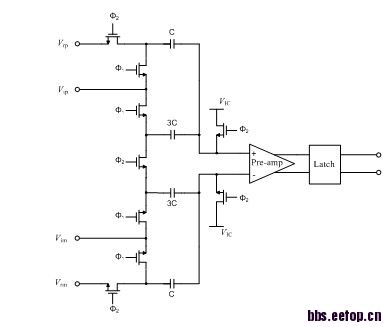

最近在做2.5bit子级时,对其中比较器的结构选择比较纠结,看到的一些论文都是用开关电容比较器结构,个人觉得首先会给前级带来很大的负载电容,尤其是2.5bit的比较器达到6个。其次分析发现这种比较器的时钟相不能简单的用Q1 Q2控制就可以的,而看论文里基本都是直接用Q1 Q2,然后进行些诸如电荷守恒之类的原理性分析,就直接上图了,不知道是否我的分析有问题。如果选用其他结构的话,对前级的负载效应会减小许多,但失调电压又比较大,可能要用到预放大器才行。

如果有哪位之前做过或正在做这方面的研究,请给一些建议,或者有相关的论文也可以推荐一些,多谢了

这种结构在我看到的国内pipeline论文里还是很常用的。

如果有哪位之前做过或正在做这方面的研究,请给一些建议,或者有相关的论文也可以推荐一些,多谢了

开关电容比较器?上图,再分析 。

这种结构在我看到的国内pipeline论文里还是很常用的。

这就是 正常的 pre-amp + latch结构嘛

并不像你所说的什么 开关电容比较器。呵呵

这就是开关电容比较器

它与其它比较器的区别就在于前面的那些电容及相应开关的配合,具体的分析你可以找相关论文看看。

1.5bit 典型比较器,2.5bit的稍微复杂一些

能否详示?你是指2.5bit里的比较器复杂吗,是否还用的开关电容结构呢

比较器都一样,关键是开关电容的组合,2,。5bit的要复杂一些,但是也不难的。

多谢了,我就是想了解一下对于2.5bit子级,比较器是否还可以用其他结构来实现

你可以用resistor ladder 来产生参考电压,不需要用电容来做reference interpolation

一般用preamp已经可以减小负载了,不需要开关电容吧

2.5bit sub adc用通常的预运放锁存比较器为什么不行?是因为比较器精度不够吗,如果Vref为800mV,那么比较器精度50mV足够了,这个在几十M的速度下,比较器是很容易达到的吧,为什么要用开关电容的,求解

这一点我也很理解,尝试用过 非开关电容,直接比较电压的,仿真发现,回踢噪声比较明显,在临界状态时会有来回波动,对仿真的输出结果影响较大。

那你的意思是这里还是用开关电容的ADC,因为我是单仿,基准电压也是直接给的,不用开关电容也能通过,那如果用开关电容的话,对前一级的负载还是影响蛮大的吧,对前一级功耗也会有影响了,你现在还是用开关电容的吗